**UNIVERSIDADE FEDERAL DE SANTA MARIA

CENTRO DE TECNOLOGIA

CURSO DE ENGENHARIA DE COMPUTAÇÃO**

**PORTE DO COMPILADOR SDCC PARA O

PROCESSADOR ZR16S08**

**TRABALHO DE CONCLUSÃO DE CURSO**

**Rafael Billig Tonetto**

**Santa Maria, RS, Brasil

2014**

# **PORTE DO COMPILADOR SDCC PARA O PROCESSADOR ZR16S08**

**Rafael Billig Tonetto**

Monografia apresentada à Universidade Federal

de Santa Maria

- UFSM, como requisito parcial

para obtenção do título de

**Engenheiro de Computação**

**Orientador: Prof. Carlos Henrique Barriquello**

**Santa Maria, RS, Brasil

2014**

**Universidade Federal de Santa Maria

Centro de Tecnologia

Curso de Engenharia de Computação**

A Comissão Examinadora, abaixo assinada, aprova a Monografia

**PORTE DO COMPILADOR SDCC PARA O PROCESSADOR ZR16S08**

elaborada por

**Rafael Billig Tonetto**

como requisito parcial para obtenção de título de

**Engenheiro de Computação**

**COMISSÃO EXAMINADORA**

**Carlos Henrique Barriquello, Dr.**

(Orientador)

**José Eduardo Baggio, Dr (UFSM)**

**João Baptista Martins, Dr (UFSM)**

Santa Maria, 10 de julho de 2014.

## Resumo

Monografia

Curso de Engenharia de Computação

Universidade Federal de Santa Maria

### **PORTE DO COMPILADOR SDCC PARA O PROCESSADOR ZR16S08**

AUTOR: RAFAEL BILLIG TONETTO

ORIENTADOR: CARLOS HENRIQUE BARRIQUELLO

Data e Local da Defesa: Santa Maria, 10 de julho de 2014.

Este trabalho tem como intuito o porte do compilador de código aberto SDCC (Small Device C Compiler) para o processador ZR16S08. A principal motivação deste esforço vem da observação de que comumente o compilador oficial do MCU (microcontrolador) ZR16S08 gera programas não muito eficientes, com muitas instruções redundantes e/ou desnecessárias que podem ser otimizadas. Programas otimizados são de crucial importância para sistemas embarcados, visto que geralmente não possuem muita capacidade de processamento e limitações de memória. Neste sentido, fez-se um esforço a fim de se adquirir um novo e mais eficiente compilador para o processador ZR16S08. Questões como tempo de execução e memória de programas são a base para a avaliação de desempenho em qualquer sistema computacional. Desta forma, procurou-se projetar um compilador com capacidade para reduzir tais fatores ao máximo possível. Comparações de desempenho do novo compilador com o compilador oficial foram essenciais a fim de avaliar o real aumento de performance. Assim sendo, *benchmarks* foram aplicados a fim de coletar dados através de simulações, tais como número de ciclos executados pelos programas e a quantidade de instruções geradas pelos compiladores. Os mesmos programas de teste foram utilizados com o compilador oficial do ZR16S08 e o SDCC, desta forma, uma medida confiável de melhoria do novo compilador foi confirmada para o *benchmark* utilizado no presente trabalho.

**Palavras-chave:** Microcontroladores. Compiladores. Sistemas embarcados. Desempenho.

## Abstract

This study aims to target the open source SDCC (Small Device C Compiler) compiler for the ZR16S08 processor. The main reason for this effort comes from the fact that the official ZR16S08 compiler usually generates programs that do not have a high level of performance, since the programs have many redundant and obsolete instructions that can be optimized. Optimized programs have a crucial importance for embedded systems, since they usually do not have much processing and memory capacity. In this sense, an effort was done in order to acquire a new and more efficient compiler for the ZR16S08 microcontroller. Issues such as time processing and program size are the basis for performance evaluation of any computational system. Therefore, an attempt to project a compiler able to reduce these factors as much as possible was made. Performance comparisons between the new targeted compiler and the official ZR16S08 compiler were essential in order to evaluate the real acquired improvement. Thus, benchmarks were applied in order to collect data through simulations, such as the total amount of cycles executed by both programs and their sizes. The same test programs were compiled with SDCC and ZR16 Compiler, hence, a reliable measure of improvement was confirmed for the benchmark used in this present study.

**Keywords:** Microcontrollers. Compilers. Embedded Systems. Performance.

# SUMÁRIO

|                                                         |    |

|---------------------------------------------------------|----|

| <b>INTRODUÇÃO</b> .....                                 | 7  |

| <b>1 O MICROCONTROLADOR ZR16S08</b> .....               | 9  |

| <b>1.1 Introdução</b> .....                             | 9  |

| <b>1.2 Características gerais</b> .....                 | 9  |

| 1.2.1 Organização e conjunto de instruções .....        | 9  |

| 1.2.2. Funcionalidades .....                            | 14 |

| <b>1.3 Compiladores, códigos, memória e MCU's</b> ..... | 14 |

| 1.3.1 Introdução .....                                  | 14 |

| 1.3.2 O compilador ZR16 Compiler .....                  | 15 |

| 1.3.3 Conclusão .....                                   | 20 |

| <b>2 NOÇÕES BÁSICAS SOBRE COMPILADORES</b> .....        | 22 |

| <b>2.1 Introdução</b> .....                             | 22 |

| <b>2.2 Estrutura de um compilador</b> .....             | 22 |

| 2.2.1 Análise Léxica .....                              | 23 |

| 2.2.2 Análise Sintática .....                           | 24 |

| 2.2.3 Análise Semântica .....                           | 25 |

| 2.2.4 Geração de Código Intermediário .....             | 26 |

| 2.2.5 Otimização de código .....                        | 27 |

| <b>2.3 Geração de Código</b> .....                      | 27 |

| <b>2.4 Conclusão</b> .....                              | 28 |

| <b>3 SDCC – SMALL DEVICE C COMPILER</b> .....           | 29 |

| <b>3.1 Introdução</b> .....                             | 29 |

| <b>3.2 Otimização de código do SDCC</b> .....           | 30 |

| 3.2.1 Otimizações gerais .....                          | 31 |

| 3.2.2 Otimizações específicas – <i>peephole</i> .....   | 35 |

| <b>3.3 iCode – Intermediate Code</b> .....              | 39 |

| 3.3.1 Introdução .....                                  | 39 |

| 3.3.2 Geração de código do SDCC .....                   | 40 |

| <b>4 PORTE DO SDCC PARA O ZR16S08</b> .....             | 43 |

| <b>4.1 Introdução</b> .....                             | 43 |

| <b>4.2 Emissão de instruções</b> .....                  | 43 |

| 4.2.1 Geração de atribuições .....                      | 43 |

| 4.2.2 Geração de lógica AND bit a bit .....             | 45 |

| 4.2.3 Geração de lógica complemento .....               | 46 |

| 4.2.4 Geração de comparações .....                      | 47 |

| 4.2.5 Outras funções .....                              | 50 |

| <b>4.3 Conclusão</b> .....                              | 51 |

| <b>5 RESULTADOS</b> .....                               | 52 |

| <b>5.1 Introdução</b> .....                             | 52 |

| <b>5.2 Avaliação de desempenho</b> .....                | 53 |

| 5.2.1 Teste com o <i>bubblesort</i> .....               | 53 |

| 5.2.2 Teste com o <i>heapsort</i> .....                 | 56 |

|                                                                              |           |

|------------------------------------------------------------------------------|-----------|

|                                                                              | 6         |

| 5.2.3 Avaliação do <i>peephole</i> com <i>heapsort</i> .....                 | 58        |

| <b>5.3 Avaliação de memória</b> .....                                        | <b>60</b> |

| <b>CONCLUSÕES</b> .....                                                      | <b>62</b> |

| <b>REFERÊNCIAS</b> .....                                                     | <b>63</b> |

| <b>APÊNDICES</b> .....                                                       | <b>64</b> |

| Apêndice A – Passagem de Parâmetros .....                                    | 64        |

| Apêndice B – Interrupções .....                                              | 67        |

| Apêndice C – genZr16Code completo .....                                      | 69        |

| Apêndice D – Algoritmo <i>bubblesort</i> .....                               | 73        |

| Apêndice E – Algoritmo <i>heapsort</i> .....                                 | 73        |

| Apêndice F – Algoritmo CRC .....                                             | 74        |

| Apêndice G – <i>Bubblesort</i> compilado pelo SDCC com <i>peephole</i> ..... | 74        |

| Apêndice H – <i>Bubblesort</i> compilado pelo SDCC sem <i>peephole</i> ..... | 76        |

| Apêndice I – <i>Bubblesort</i> compilado pelo ZR16 Compiler.....             | 77        |

| Apêndice J – <i>Heapsort</i> compilado pelo SDCC com <i>peephole</i> .....   | 79        |

| Apêndice K – <i>Heapsort</i> compilado pelo SDCC sem <i>peephole</i> .....   | 80        |

| Apêndice L – <i>Heapsort</i> compilado pelo ZR16 Compiler .....              | 82        |

| Apêndice M – CRC compilado pelo SDCC com <i>peephole</i> .....               | 85        |

| Apêndice N – CRC compilado pelo SDCC sem <i>peephole</i> .....               | 86        |

| Apêndice O – Apêndice O – CRC compilado pelo ZR16 Compiler .....             | 86        |

# INTRODUÇÃO

O presente trabalho tem o intuito de portar o compilador Small Device C Compiler (SDCC) para o processador ZR16S08. Este microcontrolador trata-se do primeiro MCU desenvolvido genuinamente no Brasil. Foi projetado na SMDH (Santa Maria Design House) e será discutido no capítulo 1. Neste contexto, portar significa adaptar ou estender o número de microcontroladores atualmente suportado pelo SDCC para o MCU acima citado. A principal motivação deste porte é a obtenção de um compilador capaz de gerar programas eficientes, que possuem tempo de execução e número de instruções tão pequenos quanto possível.

É importante que compiladores para sistemas embarcados otimizem bem seus códigos, pois os microcontroladores geralmente possuem capacidade de processamento e tamanho de memória limitados. Visto que o SDCC é um ótimo compilador otimizador e pelo fato de ser de código aberto, o mesmo foi escolhido como compilador alternativo para o MCU ZR16S08, já que, o compilador oficial deste microcontrolador não é otimizador.

Uma breve apresentação das características gerais do ZR16S08 será feita no capítulo 1. Como será apresentado também neste capítulo, o compilador oficial do ZR16S08 (ZR16 Compiler) não gera códigos muito eficientes. Nota-se que tal compilador gera um elevado número de instruções desnecessárias e/ou redundantes.

Visto que este trabalho se trata sobre compiladores, o capítulo 2 faz uma breve discussão sobre os conceitos básicos que os concernem. Este capítulo não faz nenhuma análise aprofundada sobre o assunto, porém, os conceitos fundamentais serão apresentados, visto que são essenciais ao entendimento do capítulo subsequente.

No capítulo 3 faz-se uma discussão e análise do compilador SDCC. Serão apresentadas as suas técnicas de otimização e geração de código. Este capítulo é fundamental ao entendimento do capítulo seguinte.

No capítulo 4 tem-se a descrição de como foi feito o porte do SDCC para o processador ZR16S08. Nesta etapa, será ilustrado como foram implementados os algoritmos responsáveis pela geração de algumas instruções, como atribuições, AND bit a bit (&), complemento (~) e comparações (== e !=).

O objetivo principal deste trabalho, além de obter o porte do compilador, é

fazer uma avaliação de desempenho considerando o tempo de execução e tamanho dos programas compilados pelo SDCC. Para tal, foi aplicado um *benchmark* para fins de comparação de desempenho dos programas compilados com o SDCC e ZR16 Compiler.

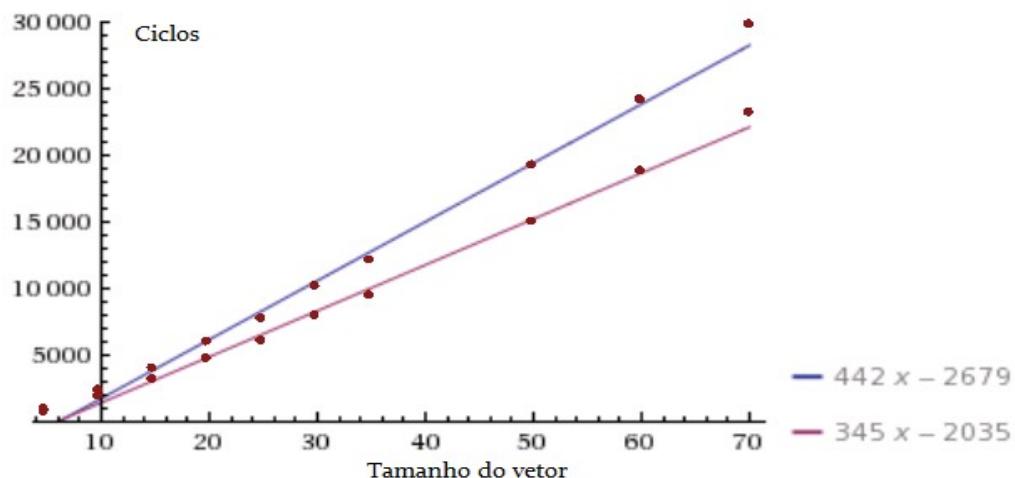

No capítulo 5 estão expostos os resultados das comparações acima citadas. Foram tabelados e ilustrados com gráficos o número de ciclos tomados pelos programas compilados pelo SDCC e ZR16 Compiler bem como os tamanhos dos programas gerados por ambos os compiladores.

# 1 O MICROCONTROLADOR ZR16S08

## 1.1 Introdução

O conhecimento das características básicas do MCU ZR16S08 é necessário a fim fazer o porte para o compilador SDCC, bem como fazer a análise do aumento ou diminuição de desempenho obtido do compilador portado.

Nesta seção será feita uma breve apresentação descrevendo a arquitetura, organização, conjunto de instruções e modos de endereçamento do processador.

É essencial ter um conhecimento prévio do conjunto de instruções e modos de endereçamento do processador para gerar as instruções corretamente e, se possível, otimizá-las, durante a fase do porte do compilador.

## 1.2 Características gerais

### 1.2.1 Organização e conjunto de instruções

O ZR16S08 é um processador de 8 bits RISC (*Reduced Instruction Set Computer* ou *Computador com um Conjunto Reduzido de Instruções*) de arquitetura Harvard que opera em uma frequência de 4 MHz.

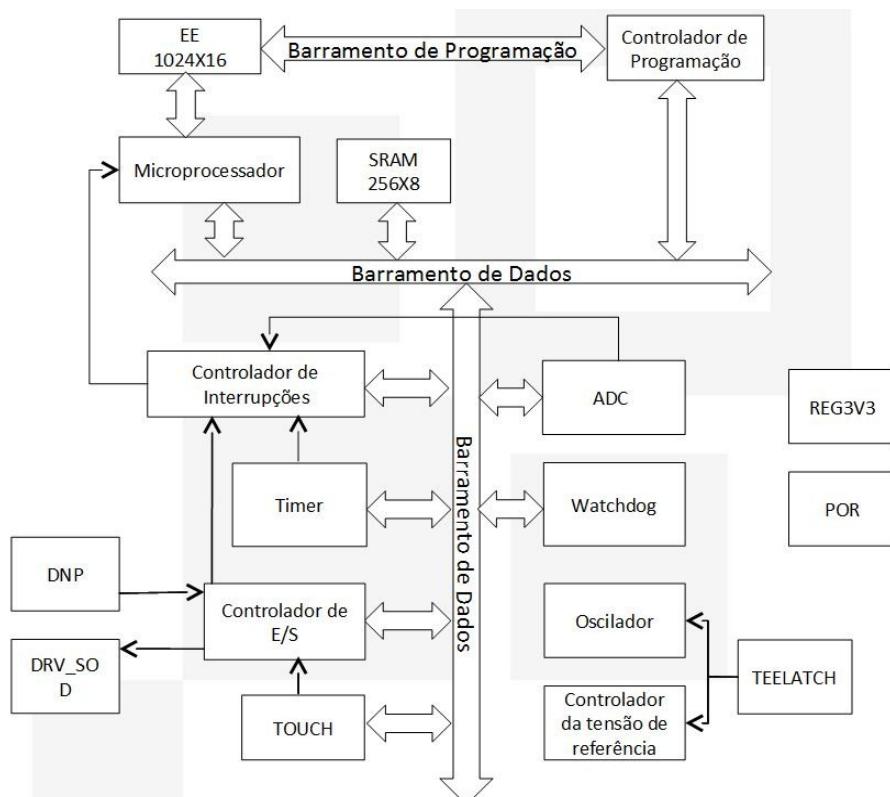

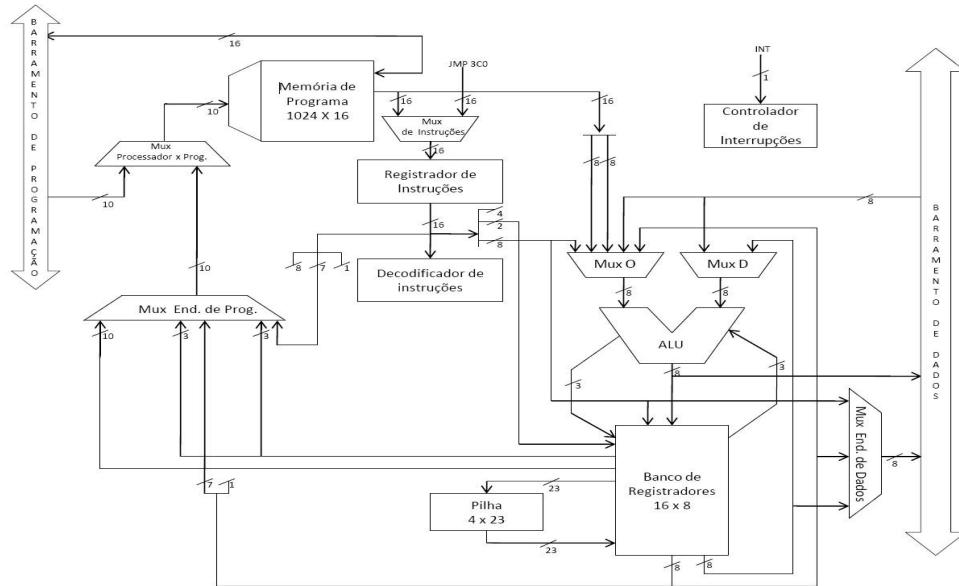

Possui 24 instruções, mostradas no quadro 1.1. Tem um banco de 16 registradores, sendo 13 de uso geral. Possui uma memória EEPROM (*Electrically Erasable Programmable Read-Only Memory* ou *Memória Eletricamente Apagável e Programável Somente Leitura*) de 1024 X 16 bits e uma memória RAM (*Random Access Memory* ou *Memória de Acesso Aleatório*) de 256 x 8 bits. Também possui uma pilha de 4 posições e tem suporte a interrupções. A figura 1.1 mostra o diagrama de blocos ilustrando as funcionalidades do processador, e.g., conversor A/D e Timer. A figura 1.2 ilustra a organização geral do ZR16S08.

As instruções do processador são gravadas na EEPROM (memória de programa), sendo possível gravar 1024 instruções de 16 bits cada. Por questões de projeto, esta memória é dividida em 8 partições (páginas) de 128 x 16 bits. Cada página pode ser acessada de acordo com os bits p0, p1 e p2 do registrador R14.

A memória RAM de 256 x 8 bits é responsável por guardar os dados do programa e só pode ser lida ou escrita pelo registrador R0, segundo os modos de endereçamento mostrados no quadro 1.2.

De acordo com o quadro 1.3, os bits 11 e 10 são responsáveis por definir o modo de endereçamento do valor à esquerda da instrução (e.g., 00 faz referência ao valor do registrador). Os bits 9 e 8 definem o modo de endereçamento do valor direito da instrução (e.g., 11 significa valor imediato).

Os bits 12-15 das instruções definem os *opcodes* das operações (e.g., a instrução MOV tem *opcodes* 1101). O quadro 1.6 mostra os *opcodes* para cada uma das instruções do MCU.

O quadro 1.2 mostra como o hardware decodifica a instrução MOV. Os bits que identificam o *opcode*, modo de endereçamento, origem e destino são os *mesmos* para as instruções AND, OR, XOR, ADD, SUB e CMP. Neste contexto, *mesmos*, não significa que os bits tem o mesmo valor, mas sim, que ocupam a mesma posição na instrução.

Figura 1.1 - Esquema geral do processador ZR16S08.

(Fonte: SMDH)

Figura 1.2 - Organização do processador ZR16S08.

(Fonte: SMDH)

Dos 16 registradores do processador, 13 são de uso geral (R0 a R12). Sabendo-se que o processador possui memória de programa de 1024 posições, precisa-se de um *program counter* (PC) de 10 bits, desta forma, o registrador R13 contém os 8 primeiros bits do PC sendo que os outros dois bits estão no R14, como ilustra o quadro 1.4.

| Instruction Set  |                           | Expression usage only (DV) |                                  | Registers      |                      |

|------------------|---------------------------|----------------------------|----------------------------------|----------------|----------------------|

| MOV              | move                      | =                          | attribution                      | r0             | General use register |

| ADD              | addition                  | +                          | addition                         | r1             | General use register |

| SUB              | subtraction               | -                          | subtraction                      | r2             | General use register |

| CMP              | compare                   | /                          | division                         | r3             | General use register |

| MVS              | move short                | *                          | multiply                         | r4             | General use register |

| INC              | incremental               | &                          | logical and                      | r5             | General use register |

| DEC              | decremental               |                            | logical or                       | r6             | General use register |

| AND              | bitwise and               | ^                          | logical xor                      | r7             | General use register |

| OR               | bitwise or                | ~                          | logical not                      | r8             | General use register |

| XOR              | bitwise xor               | sl                         | shift left (sl, sl2, ..., sl15)  | r9             | General use register |

| ROT              | rotate                    | sr                         | shift right (sr, sr2, ..., sr15) | r10            | General use register |

| SHL              | logical shift             | (                          | parenthesis                      | r11            | General use register |

| SHA              | arithmetic shift          | )                          | parenthesis                      | r12            | General use register |

| RET              | return                    |                            |                                  | r13            | General use register |

| RETC             | return and not hint       |                            |                                  | PC             | PC & Control         |

| RETZ             | return and hint=0         |                            |                                  | r14            | Control & Flags      |

| RETS             | return and hint=1         |                            |                                  | r15            |                      |

| JMP              | jump                      |                            |                                  |                |                      |

| CALL             | call                      |                            |                                  |                |                      |

| JZ               | jump if Z                 |                            |                                  |                |                      |

| JNZ              | jump if not Z             |                            |                                  |                |                      |

| JC               | jump if C                 |                            |                                  |                |                      |

| JVP              | jump if V_P               |                            |                                  |                |                      |

| DJNZ             | dec reg and jump if not Z |                            |                                  |                |                      |

| Directives       |                           | Data Memory                |                                  | Program Memory |                      |

| ORG              | origin – set address      | 256 x 8 bits               |                                  | 256 x 8 bits   |                      |

| DC               | define constant           |                            |                                  |                |                      |

| DV               | define variable           |                            |                                  |                |                      |

| DA               | define address            |                            |                                  |                |                      |

| DR               | define register           |                            |                                  |                |                      |

| Special features |                           |                            |                                  |                |                      |

| Macro            | macro - replace code      |                            |                                  |                |                      |

| \$               | current prog mem pos      |                            |                                  |                |                      |

| warning_on       | enable warning            |                            |                                  |                |                      |

| warning_off      | disable warning           |                            |                                  |                |                      |

Quadro 1.1 - Conjunto de instruções do processador ZR16S08

(Fonte: SMDH)

| Bit | Opcode<br>[15:12] | Destino/IO<br>[11:10] | Origem |             | Assembler         |

|-----|-------------------|-----------------------|--------|-------------|-------------------|

|     |                   |                       | [9:8]  | [7:3] [4:0] |                   |

| MOV | 1101              | 00                    | 0 0    | rd ro       | mov rd,ro         |

|     |                   |                       | 0 1    | rd (ro)     | mov rd,(ro)       |

|     |                   |                       | 1 0    | (end)       | mov r0, (end)     |

|     |                   |                       | 1 1    | imediato    | mov r0,imediato   |

|     |                   | 01                    | 0 0    | (rd) ro     | mov (rd),ro       |

|     |                   |                       | 0 1    | (rd) (ro)   | mov (rd),(ro)     |

|     |                   |                       | 1 0    | (end)       | mov (r0), (end)   |

|     |                   |                       | 1 1    | imediato    | mov (r0),imediato |

|     |                   | 10                    | 0 0    | (end)       | mov (end),r0      |

|     |                   |                       | 0 1    | (end)       | mov (end),(r0)    |

|     |                   |                       | 0 0    | (end)       | mov io (end),r0   |

|     |                   |                       | 0 1    | (end)       | mov io r0, (end)  |

|     |                   | 11                    | 1 0    | (rd) ro     | mov io (rd), ro   |

|     |                   |                       | 1 1    | rd (ro)     | mov io rd,(ro)    |

Quadro 1.2 - Decodificação da instrução MOV.

(Fonte: SMDH)

O quadro 1.6 mostra os *opcodes* para cada instrução do processador.

| bit 11 | bit 10 | bit 9 | bit 8 | Endereçamento           | bit 7 | bit 6 | bit 5 | bit 4 | bit 3           | bit 2 | bit 1 | bit 0           |

|--------|--------|-------|-------|-------------------------|-------|-------|-------|-------|-----------------|-------|-------|-----------------|

| 0      | 0      | 0     | 0     | r_destino, r_origem     |       |       |       |       | num reg_destino |       |       | num _reg_origem |

| 0      | 0      | 0     | 1     | r_destino, (r_origem)   |       |       |       |       | num reg_destino |       |       | num _reg_origem |

| 0      | 0      | 1     | 0     | r0, (end)               |       |       |       |       |                 |       |       | endereço        |

| 0      | 0      | 1     | 1     | r0, imediato            |       |       |       |       |                 |       |       | imediato (*)    |

| 0      | 1      | 0     | 0     | (r_destino), r_origem   |       |       |       |       | num reg_destino |       |       | num _reg_origem |

| 0      | 1      | 0     | 1     | (r_destino), (r_origem) |       |       |       |       | num reg_destino |       |       | num _reg_origem |

| 0      | 1      | 1     | 0     | (r0),(end)              |       |       |       |       |                 |       |       | endereço        |

| 0      | 1      | 1     | 1     | (r0),imediato           |       |       |       |       |                 |       |       | imediato (*)    |

| 1      | 0      | 0     | 0     | (end),r0                |       |       |       |       |                 |       |       | endereço        |

| 1      | 0      | 0     | 1     | (end),(r0)              |       |       |       |       |                 |       |       | endereço        |

Quadro 1.3 - Modo de endereçamento do ZR16 (não válido para ROT, SHL e SHA).

(Fonte: SMDH)

| Special Registers |       |       |       |       |       |       |       |       |

|-------------------|-------|-------|-------|-------|-------|-------|-------|-------|

|                   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| r15               | Z     | C     | V_P   | uf1   | uf0   | uc    | e/d   | hint  |

| r14               | mp    | p2    | p1    | p0    | ppc9  | ppc8  | PC9   | PC8   |

| r13               | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

Quadro 1.4 - Registradores de uso não geral.

(Fonte: SMDH)

O registrador R15 é condicional e guarda informações a respeito da última instrução executada, como valor nulo ( $Z = 1$ ) ou *carry* ( $C = 1$ ). O bit *hint* é utilizado para habilitar interrupções.

O quadro 1.5 ilustra a funcionalidade de cada um dos bits dos registradores

R13, R14 e R15.

Segundo o *ZR16S08 User Guide* (2013, p.11) “mp=1 acessa a memória de programa quando usando as instruções MOV Rd, (Ro) ou MOV R0, (end)”. Este bit pode ser usado para acessar variáveis do tipo `const`, que são alocadas em memória de programa.

| Description |             |                                                                                                             |

|-------------|-------------|-------------------------------------------------------------------------------------------------------------|

| PC          | PC9 - PC0   | PC (program counter) bits (10)                                                                              |

| Control     | mp          | mp=1 indicates use of Program Memory. mp=0 indicates use of data memory. Inst: MOV rd,(ro) or MOV r0,(addr) |

| Control     | p2 - p0     | if mp=1 indicates the partition to be used (4 partitions = 2 bits)                                          |

| Control     | ppc9 - ppc8 | indicates the next bits 9 and 8 for PC if instruction in use changes the content of PC                      |

| Flag        | Z           | system flag ZERO                                                                                            |

| Flag        | C           | system flag CARRY                                                                                           |

| Flag        | V_P         | system flag OVERFLOW or PARITY                                                                              |

| Flag        | uf1 - uf0   | user flags                                                                                                  |

| Control     | uc          | uc=1 indicates Carry must be used for instructions ADD, SUB, CMP and ROT                                    |

| Control     | e/d         | indicates the shift for bits on instructions ROT, SHL and SHA. (e/d=1) LEFT / (e/d=0) RIGHT                 |

| Control     | hint        | hint=1 interrupt enabled / hint=0 interruptions are disabled.                                               |

Quadro 1.5 - Funcionalidade dos bits dos registradores R13, R14 e R15.

(Fonte: SMDH)

| Instrução             | Bit 15 a 12 | Outros    |

|-----------------------|-------------|-----------|

| JMP                   | 0000        | -         |

| JZ, JNZ, JC, JVP      | 0001        | -         |

| CALL                  | 0010        | -         |

| RET, RETC, RETS, RETZ | 0011        | Bit 7 =1  |

| MVS                   | 0011        | Bit 7 = 0 |

| AND                   | 0100        | -         |

| OR                    | 0101        | -         |

| XOR                   | 0110        | -         |

| CMP                   | 0111        | -         |

| ADD                   | 1000        | -         |

| SUB                   | 1001        | -         |

| ROT                   | 1010        | -         |

| SHL                   | 1011        | -         |

| SHA                   | 1100        | -         |

| MOV                   | 1101        | -         |

| DJNZ                  | 1110        | -         |

| INC                   | 1111        | Bit 8 = 0 |

| DEC                   | 1111        | Bit 8 = 1 |

Quadro 1.6 - Opcodes das instruções do ZR16S08.

(Fonte: SMDH)

A memória de programa do ZR16 é dividida em 8 partições de 128 x 16 bits. Desta forma, os 3 bits p0, p1 e p2 (quadro 1.4) indicam qual partição deve ser acessada.

Os bits ppc9-ppc8 são utilizados para indicar o próximos bits 8 e 9 do PC (pc8 e pc9) caso a instrução sendo executada seja de desvio.

### 1.2.2. Funcionalidades

Além das memórias de programa e dados, o ZR16S08 possui um bloco de memória de 256 x 8 bits para entrada e saída de sinais digitais e analógios que fornecem recursos como:

- a) Timer para disponibilizar funções de temporização;

- b) Controlador de interrupções (ver Apêndice B);

- c) Watchdog;

- d) Conversor A/D;

- e) Touch controller (sensor de toque).

## 1.3 Compiladores, códigos, memória e MCU's.

### 1.3.1 Introdução

Até então foram mostradas características básicas do processador ZR16S08. Nesta seção, será ilustrado o problema que o corrente trabalho tem o intuito de resolver: a geração de códigos mais eficientes para o MCU ZR16S08.

O ZR16S08 possui um compilador C, que como será ilustrado, não gera códigos muito eficientes. O processo de compilação não otimiza o código e acaba gerando muitas redundâncias e instruções não necessárias.

No decorrer do capítulo, serão ilustrados códigos escritos em C e os seus respectivos códigos compilados pelo processador oficial do ZR16S08. Observando-se os códigos compilados e simulando-os, pode-se discutir questões como o tamanho do programa gerado e o número de ciclos necessários para o microcontrolador executar o programa.

O processo de gerar códigos eficientes para microcontroladores é importante, pois geralmente possuem memória de programa e de dados pequena, bem como baixa capacidade de processamento. Por esta razão, é de suma importância que os códigos para sistemas embarcados sejam otimizados: quanto menor o tamanho do programa e menor o número de ciclos necessários para a sua execução, melhor será o desempenho do microcontrolador.

Aho (2006, p.327), afirma que "...algumas medidas de custo comuns são o tempo de compilação, o tamanho, o tempo de execução e o consumo de energia do código objeto". Compiladores otimizadores para sistemas embarcados podem ser de grande utilidade neste aspecto. Por esta, dentre outras razões, o compilador SDCC foi escolhido como alternativa para a resolução do problema do compilador oficial do ZR16S08. O SDCC será discutido no capítulo 3.

### 1.3.2 O compilador ZR16 Compiler

É importante saber os tipos e tamanhos de dados suportados pelo ZR16 Compiler a fim de entender o modo que as instruções são emitidas e a maneira que o compilador escreve os dados na memória. O quadro 1.7 ilustra tais tamanhos, bem como os intervalos de valores.

| Type                  | Bits | Range          | Bytes |

|-----------------------|------|----------------|-------|

| <b>unsigned char</b>  | 8    | 0 : 255        | 1     |

| <b>signed char</b>    | 8    | -128 : 127     | 1     |

| <b>unsigned byte</b>  | 8    | 0 : 255        | 1     |

| <b>signed byte</b>    | 8    | -128 : 127     | 1     |

| <b>unsigned int</b>   | 16   | 0 : 65535      | 2     |

| <b>signed int</b>     | 16   | -32768 : 32767 | 2     |

| <b>unsigned short</b> | 16   | 0 : 65535      | 2     |

| <b>signed short</b>   | 16   | -32768 : 32767 | 2     |

Quadro 1.7 - Tipos de dados suportados pelo compilador ZR16S08

(Fonte: SMDH)

Como exemplo inicial, tem-se o código da figura 1.3 escrito em C. O respectivo código compilado pelo ZR16 Compiler está exposto na figura 1.4.

No código compilado, ';' denota comentário. Deve-se lembrar que somente o registrador R0 pode ler e escrever na memória.

```

1 char x;

2

3 void main ()

4 {

5     x = 0;

6     x++;

7 }

```

Figura 1.3 - Exemplo de código a ser analisado.

É fácil perceber o grande número de instruções não necessárias emitidas pelo compilador. Um código abstrato, otimizado, que não é gerado pelo compilador, é mostrado na figura 1.5 para fins de comparação.

```

11 ; x foi alocado no endereço 2

12

13 MOV R0 , 0

14 MOV (2) , R0      ; x = 0

15 MOV R0 , (2)      ; R0 = 0

16 MOV R2 , R0      ; R2 = 0

17 MOV R3 , R2      ; R3 = R2 = 0

18 MOV R0 , 1        ; R0 = 1

19 ADD R3 , R0      ; R3 = 1

20 MOV R0 , R3      ; R0 = 1

21 MOV (2) , R0      ; x = 1

```

Figura 1.4 - Código da figura 1.3 gerado pelo ZR16 Compiler.

Analizando o código emitido pelo compilador, nota-se que as linhas 13 e 14 fazem a atribuição  $x=0$  da maneira mais otimizada possível. Porém, o comando de incremento não é otimizado, nota-se que o compilador faz a alocação de três registradores, porém pode-se incrementar um valor de memória utilizando somente um registrador. A linha 15 é desnecessária, visto que não está mudando o valor de R0. A figura 1.5 ilustra de maneira mais clara como o programa poderia ter sido compilado sem os problemas acima citados. Um código ainda mais otimizado (o mais otimizado possível) é mostrado na figura 1.6. Neste caso, o código foi gerado pelo compilador SDCC.

```

25 MOV R0 , 0

26 MOV (2) , R0

27 ADD R0 , 1

28 MOV (2) , R0

```

Figura 1.5 - Otimização do código da figura 1.4.

```

31 MOV R0 , 1

32 MOV (2) , R0

```

Figura 1.6 - Otimização do código da figura 1.5 (gerado pelo SDCC).

O compilador SDCC possui natureza *interpretativa*. No caso do exemplo atual, o SDCC interpretou, em tempo de compilação, que a única instrução útil do código é a atribuição  $x=1$ .

Sempre que possível, o SDCC calculará os resultados de expressões como a do exemplo acima em tempo de compilação. Isto acarreta em códigos mais eficientes. Além da parte interpretativa, o SDCC aplica várias técnicas de otimização, que serão discutidas no capítulo 3.

Códigos mais eficientes são códigos menores e/ou que executam em um menor número de ciclos, por esta razão, o número de ciclos de execução pode ser usado como referência na medida de desempenho dos compiladores. Para executar o código da figura 1.3, o compilador original do ZR16S08 requer 10 ciclos, já o código compilado pelo SDCC faz as mesmas operações em apenas 2 ciclos.

Se a medida de desempenho a ser tomada for o tamanho do programa, o SDCC geralmente será melhor. No exemplo acima, o código do ZR16 Compiler gerou um código de 18 Bytes (9 instruções), valor muito alto se comparado com os 2 Bytes gerados pelo SDCC (2 instruções).

A fim de ilustrar melhor o desempenho ruim do ZR16 Compiler, será mostrado mais um exemplo de como o código ilustrado na figura 1.7 é compilado. Neste caso, as variáveis são do tipo volátil, significando que o SDCC não fará qualquer operação em tempo de compilação. Os resultados só podem ser calculados em tempo de execução. Pois estão associados a portas de entrada do microcontrolador, que podem ter seus valores alterados a qualquer momento.

```

1 volatile int x , y , z;

2

3 void main ()

4 {

5     x = y&z;

6 }

```

Figura 1.7 - Operação AND bit a bit.

As figuras 1.8 e 1.9 mostram os códigos gerados pelo ZR16 Compiler e pelo SDCC, respectivamente. Deve-se ter em mente que, segundo o quadro 1.7, variáveis inteiras possuem 16 bits. Para fazer operações que requerem leitura e/ou escrita de tais variáveis deve-se ler e/ou escrever a variável em duas etapas: uma para a parte baixa, outra para a parte alta, pois os registradores do ZR16S08 são de 8 bits.

Novamente, nota-se a grande diferença no tamanho dos códigos gerados pelos dois compiladores. O ZR16 Compiler gerou um código de 24 Bytes (12 instruções) que são executadas em 16 ciclos. Já o SDCC gerou um código com 12 Bytes (6 instruções) que são executadas em 10 ciclos.

```

12 ; x_L: parte baixa de x: MEM(2)

13 ; x_H: parte alta de x:  MEM(3)

14 ; y_L: parte baixa de y: MEM(4)

15 ; y_H: parte alta de y:  MEM(5)

16 ; z_L: parte baixa de z: MEM(6)

17 ; z_H: parte alta de z:  MEM(7)

18

19 MOV R0 , (4)    ; R0 <- y_L

20 MOV R2 , R0    ; R2 <- R0

21 MOV R0 , (5)    ; R0 <- y_H

22 MOV R3 , R0    ; R3 <- R0

23 MOV R0 , (6)    ; R0 <- z_L

24 AND R2 , R0    ; R2 <- y_L & z_L

25 MOV R0 , (7)    ; R0 <- z_H

26 AND R3 , R0    ; R3 <- y_H & z_H

27 MOV R0 , R2    ; R0 <- y_L & z_L

28 MOV (2) , R0    ; x_L <- R0

29 MOV R0 , R3    ; R0 <- y_H & z_H

30 MOV (3) , R0    ; x_H <- R0

```

Figura 1.8 - Código AND compilado pelo ZR16 Compiler.

```

33 MOV R0 , (4)    ; R0 <- y_L

34 AND R0 , (6)    ; R0 <- y_L & z_L

35 MOV (2) , R0    ; x_L <- R0

36 MOV R0 , (5)    ; R0 <- y_H

37 AND R0 , (7)    ; R0 <- y_H & z_H

38 MOV (3) , R0    ; x_H <- R0

```

Figura 1.9 - Código AND compilado pelo SDCC.

Embora o SDCC tenha diminuído o número de instruções em 50%, o número

de ciclos necessários para executar o programa diminuiu 37.5%. Isto ocorre porque as instruções com leitura de memória (e.g., `MOV R0,(4)` e `AND R0,(6)`), requerem 2 ciclos, e não 1.

Para finalizar esta seção, foi escolhido convenientemente o exemplo da figura 1.10 por questões estatísticas de otimização.

```

1 volatile x , y;

2

3 void main ()

4 {

5     x = y == 0;

6 }

```

Figura 1.10 - Comparação com zero.

Comparações com zero são estatisticamente as mais comuns, portanto, pode-se notar significativo aumento de desempenho se esta instrução for bem elaborada. A figura 1.11 ilustra o código compilado pelo ZR16 Compiler. A figura 1.12 mostra a comparação com zero gerada pelo SDCC, que é a mais eficiente possível para valores de 2 Bytes.

```

10 MVS R2 , 0

11 MOV R0 , (4)

12 MOV R4 , R0

13 MOV R0 (5)

14 MOV R5 , R0

15 MOV R0 , R5

16 AND R0 , 0x80

17 JNZ EXIT_LBL

18 MOV R0 , 0

19 CMP R5 , R0

20 JNZ EXIT_LBL

21 MOV R0 , 0

22 CMP R4 , R0

23 JNZ EXIT

24 TRUE_LBL: MVS R2 , 1

25 EXIT_LBL: MOV R0 , R2

26 MOV (2) , R0

27 MOV R0 , R3

28 MOV (3) , R0

```

Figura 1.11 - Comparação com zero gerada pelo ZR16 Compiler.

Este resultado pode ser ainda melhor notado se esta instrução for usada em *loops*, que são predominantes no tempo de execução da maioria dos aplicativos.

É fácil notar que, para valores inteiros (2 Bytes), pode-se detectar o valor zero fazendo a operação OR com suas partes alta e baixa. Esta técnica otimizada requer sempre 11 ciclos para ser executada, já o código gerado pelo ZR16 Compiler requer,

```

31 MVS  R9 , 0x00

32 MOV  R0 , (y_L)

33 OR   R0 , (y_H)

34 JNZ  THERE

35 MVS  R9 , 0x01

36 THERE: MOV R0 , R9

37 MOV  (x_L) , R0

38 MOV  R0 , 0x00

39 MOV  (x_H) , R0

```

Figura 1.12 - Comparação com zero do SDCC.

em média, 18 ciclos. Este valor é médio porque depende dos desvios, que são determinados pelo valor de *y*.

A comparação com zero do ZR16 Compiler possui 19 instruções (38 Bytes), já o SDCC compilou o código com apenas 10 instruções (20 Bytes).

### 1.3.3 Conclusão

O presente capítulo tenta apresentar as características gerais do processador ZR16S08, tanto em hardware quanto em software, bem como a baixa eficiência seu compilador.

O propósito deste trabalho é obter o porte do compilador SDCC, que será estudado no capítulo 3, a fim de gerar códigos mais eficientes para o ZR16S08 e resolver os problemas mostrados nos exemplos da seção 1.3.2.

Para tal, é necessário que sejam apresentadas noções básicas do funcionamento dos compiladores antes do SDCC ser estudado. O capítulo 2 faz uma introdução aos conceitos essenciais que os concernem.

Nenhuma análise aprofundada sobre compiladores pode ser feita em um

único capítulo, no entanto, os conceitos necessários para obter o porte do compilador ZR16S08 serão apresentados. Conceitos como código intermediário, otimização e geração de código são essenciais ao entendimento do SDCC, portanto, o capítulo 2 foi dedicado a eles.

## 2 NOÇÕES BÁSICAS SOBRE COMPILADORES

### 2.1 Introdução

A função básica dos compiladores é receber como entrada um código fonte escrito em uma linguagem de alto nível, como C, e traduzir tal código para uma linguagem de baixo nível executável pelo processador para o qual o compilador foi especificamente criado.

O processo de compilação, em poucas palavras, consiste em gerar código executável pelo processador a partir de um código fonte de nível mais alto que a linguagem de máquina.

O desenvolvimento de compiladores tem sua base na grande dificuldade encontrada pelos programadores em desenvolver programas diretamente em linguagens de máquina.

### 2.2 Estrutura de um compilador

No processo de compilação existem duas partes distintas: análise (*front-end*) e a síntese (*back-end*).

Na parte de análise, o compilador recebe o código fonte de entrada e cria um código intermediário do mesmo, bem como uma *tabela de símbolos*, que contém informações sobre o programa. É na fase de análise que o compilador irá detectar possíveis erros de sintaxe ou semântica no código fonte. Caso um destes erros ocorra, o compilador deverá informar o erro.

A parte de síntese, como o nome já informa, constrói o código objeto para o processador a partir da representação intermediária e das informações armazenadas na tabela de símbolos.

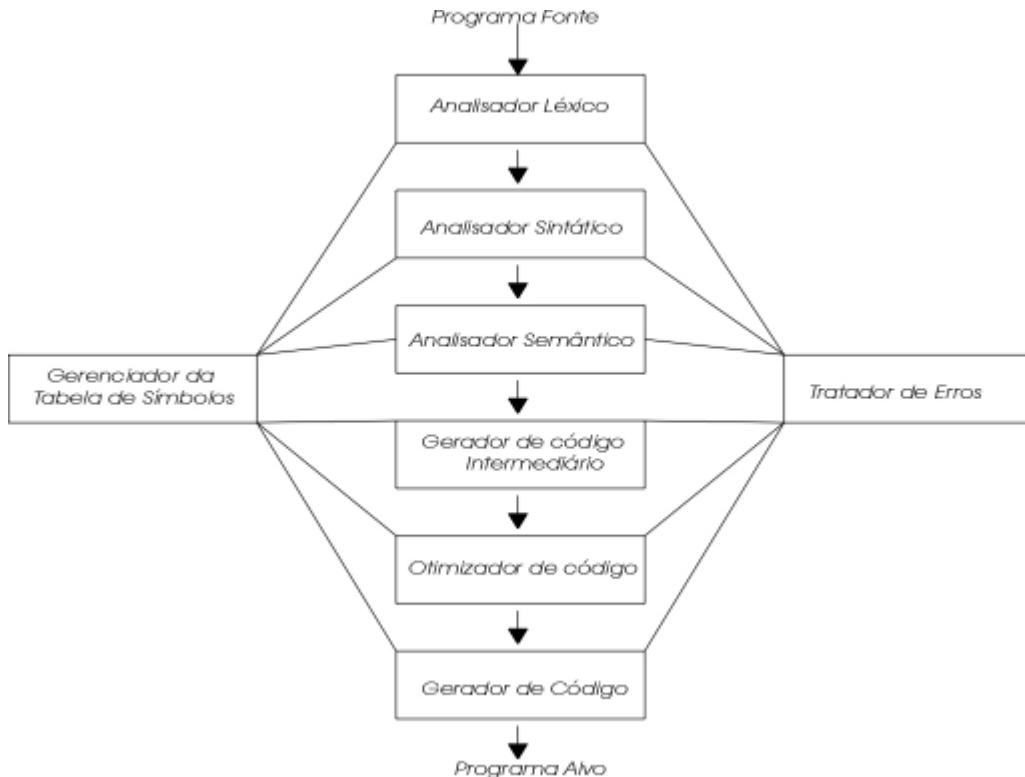

O processo de compilação é dividido em várias fases sequenciais. A saída de cada fase é uma entrada para a fase seguinte e a tabela de símbolos é usada durante todo o processo de compilação.

Uma parte de otimização de código é opcional no compilador. Esta etapa pode ser implementada de várias formas diferentes, dentre elas, a técnica de

*peephole* pode ser utilizada. Esta técnica será discutida nas próximas seções. A figura 2.1 mostra o esquema genérico do processo de compilação.

Figura 2.1 - Fases do processo de compilação.

## 2.2.1 Análise Léxica

A análise léxica é a primeira fase do compilador. Basicamente, é um algoritmo (analisador léxico) que lê o fluxo de caracteres do programa fonte e os armazena em unidades chamadas lexemas. Cada lexema é um par *<chave , valor>* chamado comumente de *token*. Os lexemas são utilizados como entrada na próxima fase da compilação, a análise sintática.

O atributo *chave*, do *token*, é um símbolo utilizado na análise sintática. O atributo *valor* é utilizado como entrada para a tabela de símbolos que retorna um valor como saída.

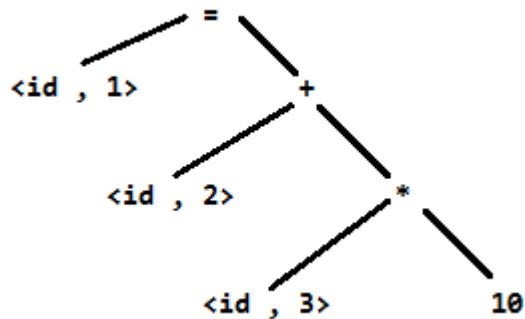

Para facilitar o entendimento do analisador léxico, suponha que um código fonte contenha a expressão

valor = valorInicial + taxa\*10 (2.1)

Os caracteres deste comando são lidos pelo analisador léxico, que ao mesmo tempo cria uma tabela de símbolos e os lexemas, na sequência:

- a) valor gera o token  $\langle id, 1 \rangle$ , sendo que  $id$  é um símbolo identificador e 1 aponta para a entrada da tabela de símbolos onde se encontra valor. A tabela manterá informações a respeito de valor, como nome e tipo;

- b) O símbolo  $=$  é mapeado para o token padrão  $\langle \Rightarrow \rangle$ . Como o símbolo  $=$  não possui valor, nome ou tipo, não precisa ser armazenado na tabela de símbolos, logo não precisa do campo de entrada para a tabela;

- c) valorInicial gera o token  $\langle id, 2 \rangle$ , onde 2 é uma entrada para a tabela de símbolos que contem informações sobre valorInicial;

- d)  $+$  gera o token padrão  $\langle + \rangle$ ;

- e) taxa gera o token  $\langle id, 3 \rangle$ , onde 3 é a entrada para a tabela de símbolos para taxa;

- f)  $*$  gera o token padrão  $\langle * \rangle$ ;

- g)  $10$  gera o token padrão  $\langle 10 \rangle$ .

Após ter sido feita a análise léxica da expressão 1.1, a seguinte sequência de tokens é gerada:

$\langle id, 1 \rangle \langle \Rightarrow \rangle \langle id, 2 \rangle \langle + \rangle \langle id, 3 \rangle \langle * \rangle \langle 10 \rangle$

A sequência de tokens é então passada para a próxima fase da compilação, a análise sintática.

## 2.2.2 Análise Sintática

Esta é a segunda fase da compilação. Nesta etapa, o analisador sintático utiliza os lexemas criados pelo analisador léxico.

O analisador sintático representa as expressões através de árvores sintáticas, em que cada nó interior da árvore representa um operador e os filhos do nó representam os operandos.

A árvore sintática deve ser construída de forma que a prioridade das operações matemáticas seja mantida. Por exemplo, como mostra a figura 2.2, o valor 10 é multiplicado a taxa antes da soma ser feita.

Figura 2.2 - Árvore de sintaxe para a expressão 2.1.

### 2.2.3 Análise Semântica

Nesta fase, o analisador semântico utiliza a árvore de sintaxe e a tabela de símbolos para verificar a consistência semântica das expressões. Por exemplo, a verificação de tipos de dados em expressões é feita nesta etapa da compilação, qualquer inconsistência nas expressões, como a atribuição de uma variável de ponto flutuante a uma variável do tipo inteira será detectada nesta fase.

O analisador coleta informações sobre os tipos e os salva na tabela de símbolos ou na própria árvore para usos subsequentes na geração de código intermediário.

## 2.2.4 Geração de Código Intermediário

O processo de gerar códigos de máquina exige que o programa fonte de alto nível seja convertido em um código intermediário antes da geração do programa executável.

As árvores sintáticas já são em si, uma forma de código intermediário, mas normalmente só são utilizadas nas duas primeiras fases da compilação.

Tradicionalmente, após as duas primeiras fases da compilação, o compilador gera um código intermediário “textual” que pode ser a linguagem de máquina do processador, ou um código de uma máquina abstrato, que deve ser convertido em código de máquina em uma próxima etapa. Um exemplo de código abstrato são os *iCodes*, do compilador SDCC, que será discutido no capítulo 3.

Mais especificamente, os códigos intermediários são *instruções de três endereços*, que constituem instruções de máquina, abstratas ou não, com três operandos cada uma. Por código de três endereços define-se toda expressão do tipo  $A = B \text{ op } C$ . Onde A, B e C representam três operandos e **op** representa uma operação. Cada operando das instruções pode ser associado a um registrador ou a endereços de memória do computador e a cada operação é associada uma variável temporária, que torna possível a execução do cálculo.

Como exemplo, a expressão 2.1 pode gerar o código intermediário

```

temp1 <= id3*10

temp2 <= id2 + temp1

id1 <= temp2

```

Onde **temp1** e **temp2** são variáveis temporárias criadas pelo compilador e **id1**, **id2** e **id3** representam **valor**, **valorInicial** e **taxa**, respectivamente.

Tendo-se a tabela de símbolos e o código intermediário, como mostra o exemplo acima, pode-se gerar as instruções *assembly* específicas para um processador alvo.

Nota-se que as instruções do código intermediário não são necessariamente de três endereços, como na atribuição **id1 <= temp2**. Mas isto não acarretará em nenhum problema no processo de geração de código, visto que é possível gerar instruções *assembly* com um único operando.

## 2.2.5 Otimização de código

Nesta etapa, o código intermediário é tomado como entrada num otimizador. Visto que o otimizador recebe o código intermediário, e não as instruções *assembly*, este tipo de otimização é independente de máquina (independente da arquitetura, organização e conjunto de instruções).

Por otimização, define-se a geração de um código menor (que utiliza menos memória) ou mais rápido que o código não otimizado (menor tempo de execução).

Um exemplo muito simplista de otimização nesta fase pode ser visto da seguinte maneira: Suponha que um compilador gere o seguinte código intermediário

```

temp1 <= id1

temp1 <= id1 + 3

```

Com a otimização, este código pode ser convertido para

```

temp1 <= id1 + 3

```

visto que a primeira instrução é desnecessária.

A etapa de otimização de código durante esta fase é opcional e varia muito de compilador a compilador. Porém, como será visto no decorrer do trabalho, a otimização de códigos representa uma grande melhoria de desempenho no programa objeto.

## 2.3 Geração de Código

Esta é a fase final da compilação. Esta etapa recebe o código intermediário (otimizado ou não) ou instruções *assembly* como entrada e gera código objeto específico para o processador. As instruções são, em seguida, interpretadas por um *montador*, que cria o arquivo objeto final. O processo de *montagem* não será abordado neste trabalho. Porém, deve-se ter em mente que as instruções de máquina geradas pelo compilador estarão diretamente relacionadas ao código

montado. Quanto mais otimizado é o conjunto de instruções *assembly* gerado pelo compilador, melhor será o código objeto.

Outro aspecto importante desta fase é a parte de associação de variáveis do programa com registradores (alocação de registradores) ou endereços de memórias. Por exemplo, o código intermediário

```

temp1 <= 3

id1 <= temp1 + 2

```

poderá ser convertido no código de máquina

```

MOV R0 , 3

ADD R0 , 2

MOV (0x00) , R0

```

onde R0 é associado a variável temporária *temp1*, somado a 2 e, em seguida, guardado no endereço de memória 0, que representa a variável id1.

## 2.4 Conclusão

Até então foram apresentados conceitos básicos sobre a estrutura e função dos compiladores. A apresentação destes conceitos, embora simplificada, é necessária para o entendimento do capítulo subsequente.

No capítulo 3 será apresentado o compilador de código aberto SDCC. Embora este compilador seja um caso específico, todas as características do funcionamento dos compiladores apresentadas no presente capítulo, como as fases de compilação (análise e síntese), geração de código intermediário e otimização são partes do funcionamento do SDCC.

## 3 SDCC – SMALL DEVICE C COMPILER

### 3.1 Introdução

SDCC é um compilador C de código aberto e redirecionável para processadores de 8 bits. O propósito geral deste compilador é gerar códigos executáveis para diferentes processadores a partir do mesmo código intermediário.

A versão atual do SDCC suporta os processadores Intel MCS51 (8031, 8032, 8051, 8052, etc.), Dallas DS80C390, Freescale HC08 (HC08 e S08), Zilog Z80 e STMicroelectronics STM8.

Basicamente, pode-se redirecionar este compilador para um processador específico a partir do código intermediário (*iCode*, ou *intermediate code*) criado pelo *front-end* do compilador.

No processo de geração de código executável, deve-se tomar como entrada uma sequência de *iCodes* que definem a sequência de instruções a serem emitidas para um processador específico e gerar uma saída com instruções para a máquina alvo.

O propósito deste trabalho é estender o número de alvos portados pelo SDCC, definindo-se um novo porte para o processador ZR16S08.

A escolha deste compilador foi feita com base na sua natureza de porte livre e ótimas técnicas de otimização de código. Como será mostrado no capítulo 4, este compilador pode gerar códigos de alta performance.

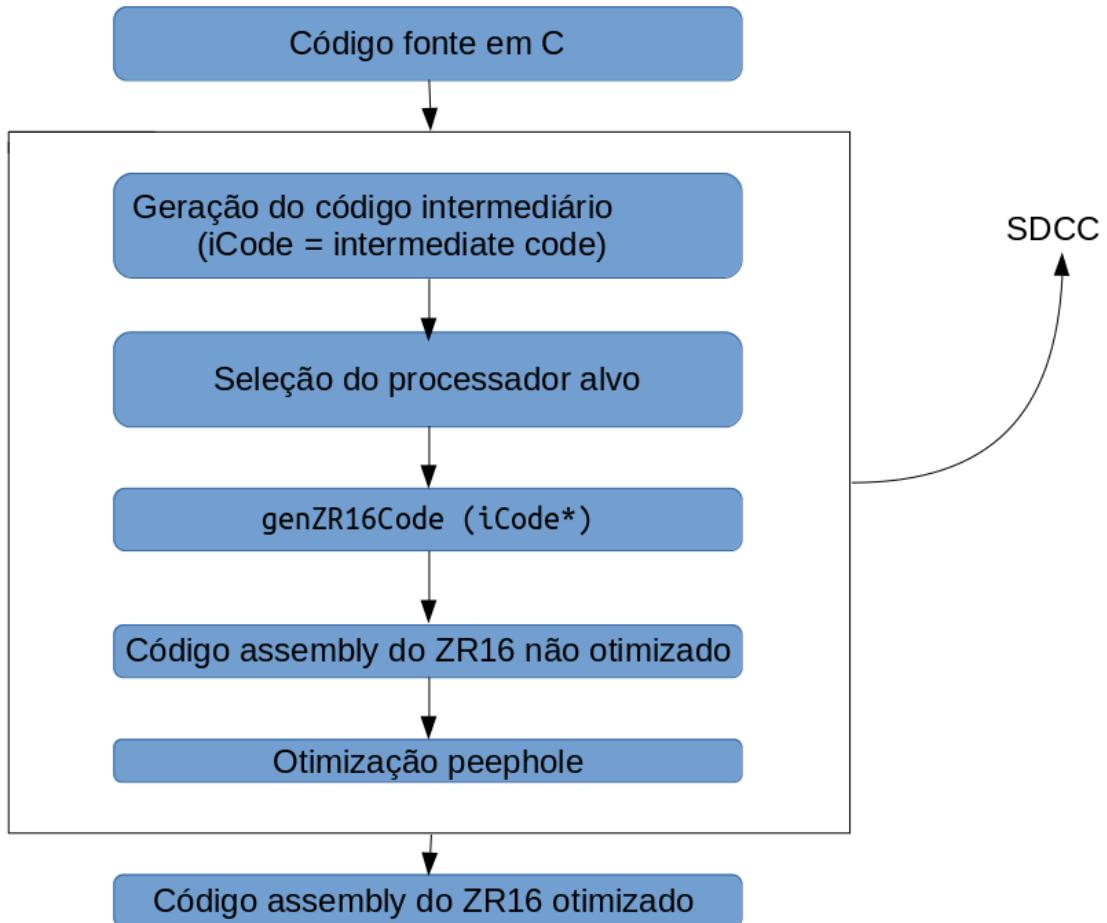

A figura 3.1 ilustra a ideia básica do funcionamento do SDCC. Após tomar-se um código fonte escrito em C como entrada e gerar-se o código intermediário, uma função específica é chamada, por meio da seleção do processador alvo, a fim de emitir as instruções necessárias e gerar o seu respectivo código *assembly*.

Após a geração do código, o mesmo pode ser otimizado pela técnica de *peephole*, que será discutida na seção 3.2.2.

A seção 3.2.1 ilustra as otimizações gerais do SDCC. Estas otimizações são gerais porque podem ser aplicadas em todos os processadores suportados pelo compilador.

Figura 3.1: Esquema geral do funcionamento do SDCC.

### 3.2 Otimização de código do SDCC

O SDCC é um compilador otimizador, pois possui várias técnicas de otimização de código, algumas otimizações são gerais e válidas para todos os portes. Estas otimizações serão apresentadas na seção 3.2.1.

A técnica de otimização mais eficiente deste compilador é o *peephole*, que não é geral e deve ser definida para cada alvo durante a criação do porte do compilador, pois esta técnica é dependente do conjunto instruções de cada processador.

Algumas técnicas de otimização gerais do SDCC são: eliminação de códigos não utilizados (*Dead-Code Elimination*), propagação de cópia (*Copy-Propagation*), otimizações de *loop* (*Loop Invariant* e *Loop Reversing*) e simplificações algébricas.

A seguir, será apresentado um exemplo do funcionamento de cada uma das técnicas citadas acima.

### 3.2.1 Otimizações gerais

#### a) *Dead-Code Elimination:*

Esta técnica evita que códigos não utilizados sejam compilados. O código da figura 3.2 mostra um exemplo de programa com código morto, a figura 3.3 mostra como o SDCC otimiza o código suprimindo todos os comandos não necessários no código.

```

1 int global;

2

3 void f ()

4 {

5     int i;

6     i = 1;          /* Dead code */

7     global = 2;      /* Dead code */

8     global = 3;

9     return;

10    global = 4;     /* Código inatingível */

11 }

```

Figura 3.2 - Programa com código morto.

Linhas de comando, como as 6, 7 e 10 da figura 3.2, são frequentemente escritas por descuido do programador. Sempre que possível, o SDCC evitará que tais códigos sejam compilados interpretando o código da figura 3.2 da maneira mostrada na figura 3.3.

```

1 int global;

2

3 void f ()

4 {

5     global = 3;

6 }

```

Figura 3.3 - Programa com código morto eliminado pelo SDCC.

b) *Copy-Propagation*:

O código mostrado na figura 3.4 mostra um exemplo de *copy-propagation* no que diz respeito a atribuições.

É necessário saber que fazer referência a variáveis significa ler um endereço de memória, acarretando em um maior número de ciclos. Para o processador ZR16S08, por exemplo, atribuir um valor direto a um endereço de memória requer, no mínimo, um ciclo, já atribuir um endereço de memória a outro requer pelo menos três ciclos.

```

1 int f ()

2 {

3     int i , j;

4     i = 10;

5     j = i;

6     return j;

7 }

```

Figura 3.4 – Copy-propagation.

As figura 3.5 mostra como o SDCC converte o código (altera a linha 5) da figura 3.4 para fins de otimização. O SDCC aplica esta modificação visto que a atribuição  $j=10$  é mais rápida que  $j=i$ , pois desta forma não há necessidade de acessar a memória e ler a variável  $i$ .

```

10 int f ()

11 {

12     int i , j;

13     i = 10;

14     j = 10;

15     return j;

16 }

```

Figura 3.5 - Código otimizado.

c) *Loop Invariant*:

Pode-se ganhar um significativo aumento de performance se esta técnica de

otimização for aplicada no código mostrado na figura 3.6.

```

1 for (i = 0 ; i < 100 ; i++)

2 {

3     f += k + l;

4 }

```

Figura 3.6 - Loop Invariant.

```

7 temp = k + l;

8

9 for (i = 0 ; i < 100 ; i++)

10 {

11     f += temp;

12 }

```

Figura 3.7 - Código transformado pelo SDCC.

Na figura 3.6, é evidente que a soma  $k+l$  é constante, desta forma, o SDCC faz a soma  $k+l$  fora do *loop* uma única vez, eliminando a necessidade de fazer tal operação em cada iteração do *loop*.

O código da figura 3.6 é modificado de acordo com a figura 3.7. Esta técnica representa um ganho muito significativo de eficiência, visto que, estatisticamente, as operações com *loop* são predominantes no tempo de execução da maioria dos programas.

#### d) *Loop Reversing*:

Esta técnica é aplicada somente em *loops reversíveis* a fim de simplificar as verificações de comparação para término do *loop*.

*Loops reversíveis* são *loops* que podem ter seus campos trocados de maneira que o resultado dos cálculos de seu bloco não sejam alterados. Por exemplo, os *loops* das figuras 3.8 e 3.9 tem a mesma funcionalidade, o valor final de *count* é o mesmo para ambos os casos.

```

1 for (i = 0 ; i < 100 ; i++)

2 {

3     count++;

4 }

```

Figura 3.8 - *Loop* reversível.

```

7 for (i = 100 ; i > 0 ; i--)

8 {

9     count++;

10 }

```

Figura 3.9 - *Loop* da figura 3.8 invertido.

O *loop* mostrado na figura 3.10 não é reversível, pois a sua inversão acarretaria em valores incorretos para o vetor *element*.

Caso o *loop* fosse invertido, a variável *i* seria iterada de 100 a 1, e não de 0 a 99, que é a maneira desejada ilustrada na figura 3.10. Isto acarretaria em um *overflow* no vetor *element* e impediria que o valor *element[0]* fosse inicializado.

```

1 for (i = 0 ; i < 100 ; i++)

2 {

3     element[i] = i;

4 }

```

Figura 3.10 - *Loop* não reversível.

Pode-se obter otimização significativa se for feita a inversão de *loops* como o mostrado na figura 3.8 visto que para cada iteração do *loop* a verificação da expressão *i > 0* é mais eficiente do que a verificação de *i < 100*, pois comparações com zero são sempre mais rápidas, pois pode-se usar instruções como *DNZ* (*decrement and jump if not zero*) ou *JZ* (*jump if zero*) .

No capítulo 1 foi mostrada a grande eficiência que o SDCC possui em detectar o valor zero.

```

6 for (i = 100 ; i > 0 ; i--)

7 {

8     element[i] = i;

9 }

```

Figura 3.11 - Loop indevidamente invertido.

O SDCC tem um conjunto específico de critérios para determinar se o *loop* é reversível ou não, são eles:

1) O *loop for* é da forma

```

for(<symbol>=<exp>;<sym>[<|<=]<exp>;[<sym>++|<sym>+= 1])

<for body> ;

```

2) <for body> não pode conter *continue* ou *break*;

3) Não pode existir chamadas de procedimentos no *loop*;

4) O valor <sym> não pode ser referenciado no corpo do *loop*;

5) Não pode haver *switch* no loop.

e) Simplificações algébricas:

O SDCC aplica várias simplificações algébricas, alguns exemplos são:

|                  |               |               |

|------------------|---------------|---------------|

| 1) $i = j + 0$   | é mudado para | $i = j;$      |

| 2) $i = j*2$     | é mudado para | $i = j << 1;$ |

| 3) $i = j/2$     | é mudado para | $i = j >> 1;$ |

| 4) $i = j - j$   | é mudado para | $i = 0;$      |

| 5) $i = 10 + 20$ | é mudado para | $i = 30.$     |

### 3.2.2 Otimizações específicas – *peephole*

Visto que se torna muito difícil gerar códigos otimizados diretamente no momento em que as instruções são emitidas pelo compilador, muitas melhorias podem ser feitas no código após o mesmo ter sido gerado.

Como afirma o *SDCC Compiler User Guide* (2014), a técnica *peephole* (otimização de janela) é uma técnica de transformação baseada em um conjunto de regras definidas pelo programador que são aplicadas pelo otimizador através de um reconhecimento de padrões. Tais regras são regras de substituição de instruções,

ou sequências de instruções, desta forma, este método é dependente da máquina alvo.

Esta técnica é feita através de uma *janela deslizante* que “varre” o conjunto de instruções não otimizado gerado pelo compilador sequencialmente. Sempre que possível, o conjunto de instruções da janela é substituído por um conjunto de instruções menor ou mais rápido.

As regras de substituição devem ser definidas pelo programador e, como já citado, são específicas para cada máquina.

Visto que o intuito deste trabalho é o porte do compilador SDCC para o processador ZR16S08, o conjunto de instruções do mesmo será utilizado para ilustrar alguns exemplos de otimização pela técnica *peephole*.

No SDCC, as regras de substituição por janela são definidas da seguinte forma:

```

replace { <alguma sequência de instruções> }

by      { <outra sequência de instruções> }

```

A fim de ilustrar o funcionamento desta técnica, suponha que o SDCC gere o código ilustrado na figura 3.12 para o processador ZR16S08:

```

69 MOV R0 , R1

70 MOV R1 , R0

```

Figura 3.12 - Exemplo de código redundante.

Após a geração do código, um otimizador pode aplicar a técnica de otimização de janela e eliminar a instrução da linha 70, mostrada na figura 3.12.

Como exemplo, a regra para eliminar a instrução redundante do exemplo acima é ilustrada na figura 3.13.

A eliminação da instrução, na verdade, é uma substituição de todo um conjunto de instruções por outro mais eficiente.

Na figura 3.13,  $\%n$  ( $n = 1, 2, \dots$ ) representa qualquer variável, registrador, valor numérico ou *label*.

```

59 replace

60 {

61     MOV %1 , %2

62     MOV %2 , %1

63 }

64 by

65 {

66     MOV %1 , %2

67 }

```

Figura 3.13 - Regra *peephole* para eliminar instrução redundante.

Outro exemplo de código que pode ser otimizado é mostrado na figura 3.14.

```

33 JNZ label_A

34 JMP label_B

35 label_A: INC R0

36 label_B: DEC R0

```

Figura 3.14 - Código pode ser melhorado com *peephole*.

Um código otimizado para este exemplo é mostrado na figura 3.15, que pode ser obtido com a regra *peephole* da figura 3.16.

```

39 JZ label_B

40 label_A: INC R0

41 label_B: DEC R0

```

Figura 3.15 - Código otimizado.

Na regra mostrada na figura 3.16, %1 e %2 representam os *labels* `label_A` e `label_B`, respectivamente. Esta regra aparenta não ter muito efeito no aumento de desempenho, pois elimina uma única instrução. Porém, as instruções de desvio mostradas acima são geralmente criadas em *loops*, desta forma pode-se observar um significativo aumento de performance em algoritmos com laços, visto que para cada iteração do *loop* tem-se uma instrução a menos a ser executada.

O SDCC aplica as regras de otimização uma por uma em sequência a partir do inicio da sequência de regras. Este processo de otimização terminará quando

```

43 replace

44 {

45     JNZ %1

46     JMP %2

47     %1:

48     %2:

49 }

50 by

51 {

52     JZ %2

53 }

```

Figura 3.16 - Transforma o código da fig. 3.15 no código da fig. 3.16.

todas as regras forem verificadas. Segundo Aho (2006, p.348) “É característica da otimização por janela que cada melhoria possa gerar oportunidades para melhorias adicionais”. Para tal, se a opção *restart* for especificada nas regras o otimizador reiniciará o processo verificação de substituição desde o início do código.

Para ilustrar o uso da opção *restart*, observe como a regra de substituição da figura 3.17 afeta as instruções da figura 3.18, não conseguíramos obter o código mais eficiente possível, visto que ainda sobrariam redundâncias.

```

11 replace

12 {

13     ADD %1 , %2

14     SUB %1 , %2

15 }

16 by {} ; Substitui por nada.

```

Figura 3.17 - Regra para eliminar instruções.

```

7 ADD R3 , R4

8 ADD R1 , R2

9 SUB R1 , R2

10 SUB R3 , R4

```

Figura 3.18 - Código a ser otimizado.

Aplicando-se a regra da figura 3.17 no código da figura 3.18, o SDCC acabaria gerando o código mostrado na figura 3.19.

```

7 ADD R3 , R4

8 SUB R3 , R4

```

Figura 3.19 - Código parcialmente otimizado.

O código ainda pode ser eliminado se a opção *restart* for especificada, como mostra a figura 3.20.

```

11 replace restart

12 {

13     ADD %1 , %2

14     SUB %1 , %2

15 }

16 by {}      ; Substitui por nada.

```

Figura 3.20 - Regra com *restart*.

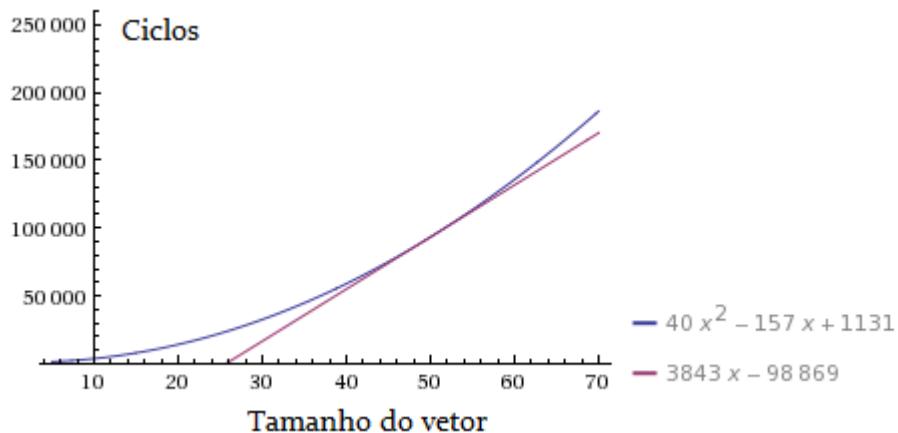

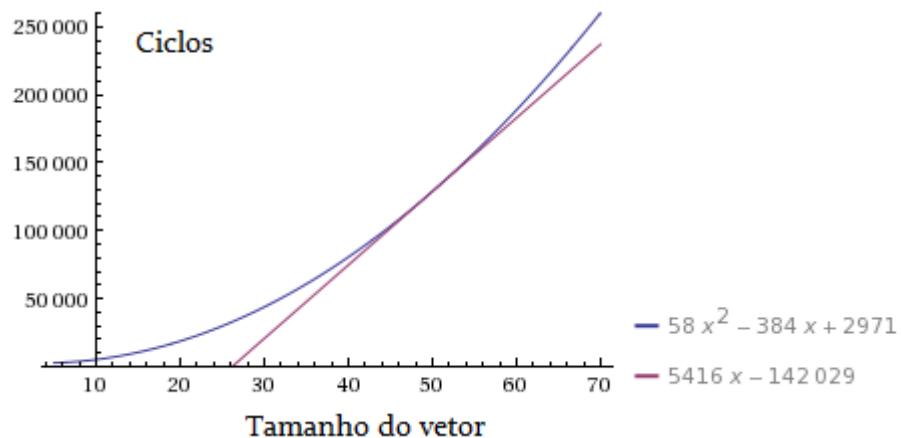

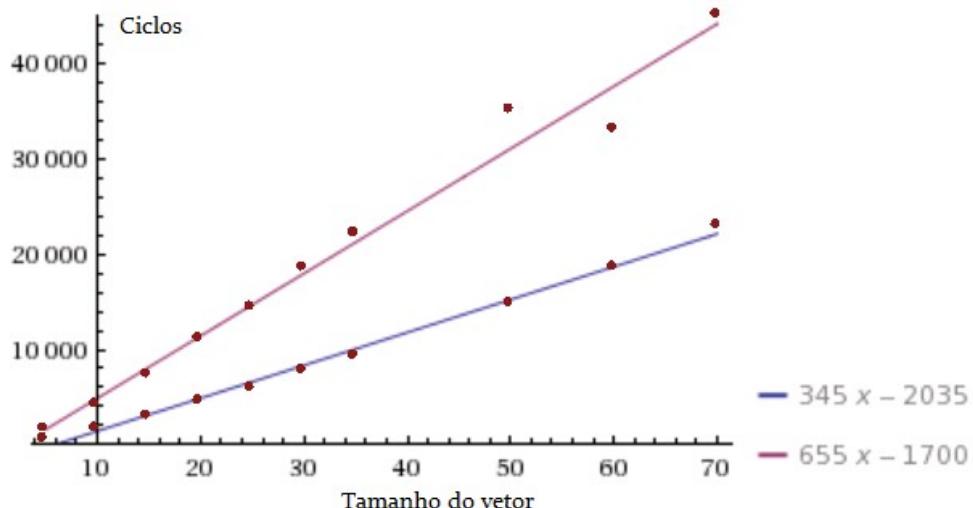

Os resultados desta técnica de otimização são muito significativos, como será mostrado posteriormente. Será apresentada uma comparação do tempo de execução do algoritmo *heapsort* com otimização *peephole* e sem a mesma para fins de comparação. Além do tamanho do programa, o número de ciclos de execução diminui significativamente se esta técnica for aplicada.

### 3.3 iCode – *Intermediate Code*

#### 3.3.1 Introdução

No processo de compilação de códigos, o SDCC quebra as instruções do código fonte a ser compilado em um formato de instruções de três endereços chamados *iCodes*. Este formato de código intermediário guarda informações sobre a operação a ser aplicada entre seus operandos. Informações sobre os operandos também são agrupadas em cada *iCode*, como o nome (endereço de memória), tipo

e tamanho, por exemplo.

### 3.3.2 Geração de código do SDCC

Para cada programa compilado, uma lista duplamente encadeada de *iCodes* é gerada de forma que o fluxo no qual as instruções são emitidas possa ser gerenciado corretamente. Cada nodo da lista representa uma instrução de três endereços que inclui uma operação que deve ser usada no processo de geração de códigos de máquina. Como é afirmado no *SDCC Compiler User Guide* (2014), a geração de código envolve traduzir estas operações em *assembly* correspondente do processador.

Para ilustrar o funcionamento dos *iCodes*, suponha o comando exemplo abaixo.

```

result = left + right;

```

Neste exemplo, o SDCC geraria um *iCode* para a geração de soma e atribuição do tipo `IC_RESULT = IC_LEFT + IC_RIGHT`. Neste *iCode* tem-se todas as informações necessárias para a geração do código de máquina. Sabendo-se a operação a ser aplicada (+) e tendo-se dados a respeito dos três operandos é possível emitir as instruções corretas para um processador alvo.

No exemplo acima, o SDCC analisaria o *iCode* da atribuição com soma e chamaria a rotina `genPlus`. Nesta rotina, deve ser implementada a lógica necessária pra a geração de soma para o processador alvo, por exemplo, a rotina `genPlus` para o processador ZR16S08 poderia emitir a sequência de instruções mostrada na figura 3.21.

```

1 MOV R0 , (left)

2 ADD R0 , (right)

3 MOV (result) , R0

```

Figura 3.21 - Código gerado pela rotina `genPlus` do ZR16S08.

A ideia básica na geração do código de máquina é percorrer toda a lista de *iCodes*, analisar a operação a ser feita por cada nó e emitir as instruções necessárias envolvendo os operandos.

O código mostrado na figura 3.22 ilustra o processo básico da geração de algumas instruções para o processador ZR16S08. Esta é a fase de *back-end* do compilador. Nela, recebe-se o código intermediário como parâmetro, gerado na fase anterior do processo de compilação. Esta é a essência do SDCC: receber a lista de *iCodes* e traduzi-la para o código de máquina correspondente.

Por questões de espaço, o código da figura 3.22 não está completo. Somente foram ilustradas algumas das funcionalidades do SDCC para propósitos de explicação do funcionamento do compilador. O código completo se encontra-se no Apêndice C.

```

1 void genZr16Code(iCode * lic)

2 {

3     iCode *ic;

4

5     /* Percorre toda a lista de iCodes e analisa cada nó. */

6     for (ic = lic ; ic ; ic = ic->next)

7     {

8

9         /* Verifica a operação a ser realizada. */

10        switch (ic->op)

11        {

12            case '=': genAssign(ic);                                /* Ex.: x = y;      (IC_RESULT = IC_RIGHT) */

13            break;

14            case '+': genPlus(ic);                                /* Ex.: x = y + z; (IC_RESULT = IC_LEFT + IC_RIGHT) */

15            break;

16            case '>': genCmpGt(ic, ifxForOp(IC_RESULT(ic), ic)); /* Ex.: x = y > z; (IC_RESULT = IC_LEFT > IC_RIGHT) */

17            break;

18            case '<': genCmpLt(ic, ifxForOp(IC_RESULT(ic), ic)); /* Ex.: x = y < z; (IC_RESULT = IC_LEFT < IC_RIGHT) */

19            break;

20            case EQ_OP: genCmpEq(ic, ifxForOp(IC_RESULT(ic), ic)); /* Ex.: x = y == z; (IC_RESULT = IC_LEFT == IC_RIGHT) */

21            break;

22            case AND_OP: genAndOp(ic);                            /* Ex.: x = y && z; (IC_RESULT = IC_LEFT && IC_RIGHT) */

23            break;

24            case '!': genNot(ic);                                /* Ex.: x = !y;      (IC_RESULT = !IC_LEFT) */

25            break;

26            case '|': genOr(ic, ifxForOp(IC_RESULT(ic), ic));   /* Ex.: x = y | z; (IC_RESULT = IC_LEFT | IC_RIGHT) */

27            break;

28            case IFX: genIfx(ic, NULL);                          /* if (IC_COND) goto IC_TRUE ou if (!IC_COND) goto IC_FALSE */

29            break;

30            case SEND: genSend(ic);                            /* Passa parâmetros por registrador (Move IC_LEFT para algum registrador alocado). */

31            break;

32            default:

33        }

34    }

35

36    /* Após a geração do código, pode-se aplicar o PeepHole para otimização. */

37

38    if (!options.nopee)

39    {

40        peepHole(&ic);

41    }

42 }

```

Figura 3.22 - Geração de instruções para cada *iCode*.

Como mostra a linha 6 do código, um *loop* percorre todos os nodos da lista de *iCodes*, ao encontrar um *iCode* com a operação '+', por exemplo, a rotina *genPlus* é chamada (linha 14). Esta rotina deve prover o algoritmo necessário para emitir as

instruções de soma para o processador alvo.

Após todo o código fonte ter sido gerado, com o fim do *loop*, uma opção de otimização pode definir se o código deve ser otimizado ou não. Se a rotina `peepHole` for chamada (linha 40), a técnica de otimização por janela é aplicada no código gerado.

## 4 PORTE SDCC PARA O ZR16S08

### 4.1 Introdução

Nesta seção será demonstrado como gerar códigos para o processador ZR16S08 a partir dos *iCodes*. A ideia básica deste capítulo é ilustrar o funcionamento do processo de como as instruções são emitidas. Por questões de espaço, não será feita uma discussão detalhada de como cada uma das funções foi implementada.

Será ilustrado como instruções comuns, como atribuição (=), AND bit a bit (&), complemento (~) e comparação podem ser implementadas para o processador ZR16S08.

Como discutido anteriormente, cada *iCode* é um código de três operandos. No processo de geração de código, deve-se extrair a operação a ser realizada do *iCode*, verificar qual função deve ser chamada (como mostra a figura 3.22) e em seguida, chamar o procedimento necessário para a emissão de código.

### 4.2 Emissão de instruções

#### 4.2.1 Geração de atribuições

A figura 4.1 mostra um exemplo simplificado de como emitir instruções de atribuição para o processador ZR16S08.

Este exemplo tem somente um propósito ilustrativo, na prática, o método `genAssign` não foi implementado da forma mostrada na figura 4.1. Vários detalhes de implementação estão ocultos e não é de interesse mostrá-los nesta sessão. Porém, é mostrado essencialmente como o método `genAssign` foi construído. O exemplo agora citado ilustra uma possível implementação para atribuição de variáveis globais. Porém, deve-se ter em mente que existem várias possibilidades de atribuição, como de valores numéricos, parâmetros, variáveis temporárias, ponteiros

e atribuições de valores com tamanhos diferentes. O método `genAssign` deve prover técnicas de geração de código para cada um destes casos.

Logo que o compilador chama a função `genZr16Code`, um *loop* começa a “percorrer” a lista de *iCodes*, ao encontrar um nodo da lista com a operação ‘=’, o método `genAssign` é chamado. O primeiro passo deste método é extrair os operandos do resultado da atribuição, e o valor a ser atribuído. Neste caso, isto nada mais é do que gerar um ponteiro para os endereços de memória do valor a ser atribuído e para o resultado.

```

1  /*

2   * genAssign(): Código responsável por gerar atribuições.

3   *

4   * Exemplo:

5   *

6   *     int x , y;

7   *     x = y;           (IC_RESULT = IC_RIGHT)

8   */

9

10 static void genAssign (iCode * ic)

11 {

12     /* Extrai resultado da operação (x). */

13     operand *result = IC_RESULT(ic);

14

15     /* Extrai o valor a ser atribuído ao resultado da operação (y). */

16     operand *right = IC_RIGHT(ic);

17

18     /* Pega o endereço de memória do resultado: Parte baixa. */

19     char *result_Addr_LOW = getOperandAddr (result , LOW);

20

21     /* Pega o endereço de memória do resultado: Parte alta. */

22     char *result_Addr_HIGH = getOperandAddr (result , HIGH);

23

24     /* Pega o endereço de memória do valor direito: Parte baixa. */

25     char *right_Addr_LOW = getOperandAddr (right , LOW);

26

27     /* Pega o endereço de memória do valor direito: Parte alta. */

28     char *right_Addr_HIGH = getOperandAddr (right , HIGH);

29

30     /* Emite instruções para o ZR16 em um arquivo de saída. */

31

32     emitcode ("MOV" , "R0 , (%s)", right_Addr_LOW);           // R0 <- (right_Addr_LOW)

33     emitcode ("MOV" , "(%s) , R0", result_Addr_LOW);           // (result_Addr_LOW) <- R0

34

35     if (AOP_SIZE (result) == 1) return;

36

37     emitcode ("MOV" , "R0 , (%s)", right_Addr_HIGH);           // R0 <- (right_Addr_HIGH)

38     emitcode ("MOV" , "(%s) , R0", result_Addr_HIGH);           // (result_Addr_HIGH) <- R0

39 }

40

```

Figura 4.1 - Exemplo simplificado da geração de atribuições para o ZR16S08.

Os comandos `IC_RESULT (iCode*)`, `IC_RIGHT(iCode*)` (linhas 13 e 16) retornam ponteiros para os operandos `result` (`x`) e `right` (`y`) da atribuição. Em

seguida, a função `getOperandAddr` retorna ponteiros para os seus respectivos endereços de memória.

Se os operandos ocuparem 2 Bytes, serão necessários dois endereços de memória para serem alocados, por este motivo, pode-se definir parâmetros `LOW` e `HIGH` que retornam os endereços dos Bytes inferior e superior, respectivamente.

Após os ponteiros para os respectivos valores do resultado e do valor atribuído terem sido alocados, só resta emitir as instruções necessárias para escrever os valores na memória do processador (linhas 32 a 38).

Note que na linha 35 do código da figura 4.1 o tamanho do resultado é verificado. Se for de 1 Byte, a rotina retorna, pois o valor do resultado ocupa somente um endereço de memória (1 Byte). Caso o tamanho do resultado seja de 2 Bytes, as linhas 37 e 38 emitem as instruções para escrever a outra metade do seu valor em outro endereço.

#### 4.2.2 Geração de lógica AND bit a bit

A figura 4.2 ilustra uma possível implementação da lógica AND (`genAnd`) bit a bit para o ZR16S08. Novamente, detalhes de implementação estão ocultos.

A lógica de implementação da função `genAnd` é similar à lógica da função `genAssign`. Primeiramente são extraídos os operandos, que neste caso são três, atribuídos os ponteiros para os seus respectivos endereços de memória e, em seguida, as instruções são emitidas.

A lógica AND das partes alta e baixa é emitida nas linhas 30 e 38, respectivamente, ficando guardadas em `R0`. O resultado das partes alta e baixa é atribuído nas linhas 31 e 39, respectivamente.

```

1  /*

2   * genAnd(): Código responsável por gerar AND bit a bit.

3   *

4   * Exemplo:

5   *

6   *     int x , y , z;

7   *     x = y & z;           (IC_RESULT = IC_LEFT & IC_RIGHT)

8   */

9

10 static void genAnd (iCode * ic)

11 {

12     operand *result = IC_RESULT(ic);    // Extrai resultado da operação (x).

13     operand *left   = IC_LEFT(ic);      // Extrai o valor esquerdo (y).

14     operand *right  = IC_RIGHT(ic);     // Extrai o valor direito(z).

15

16     char *result_Addr_LOW = getOperandAddr (result , LOW);    // Pega o endereço de memória do resultado: Parte baixa.

17     char *result_Addr_HIGH = getOperandAddr (result , HIGH);   // Pega o endereço de memória do resultado: Parte alta.

18

19     char *left_Addr_LOW  = getOperandAddr (left , LOW);        // Pega o endereço de memória do valor esquerdo: Parte baixa.

20     char *left_Addr_HIGH = getOperandAddr (left , HIGH);       // Pega o endereço do valor esquerdo: Parte alta.

21