**UNIVERSIDADE FEDERAL DE SANTA MARIA

CENTRO DE TECNOLOGIA

CURSO DE ENGENHARIA DE COMPUTAÇÃO**

**ACOPLAMENTO E VALIDAÇÃO FUNCIONAL

DO SISTEMA RECONFIGURÁVEL DIM**

**TRABALHO DE CONCLUSÃO DE CURSO**

**Sandro Pedroso Jacobsen**

**Santa Maria, RS, Brasil**

**2014**

# **ACOPLAMENTO E VALIDAÇÃO FUNCIONAL DO SISTEMA RECONFIGURÁVEL DIM**

**por**

**Sandro Pedroso Jacobsen**

Trabalho de Conclusão de Curso apresentado ao Programa de Graduação em Engenharia de Computação, da Universidade Federal de Santa Maria (UFSM), RS, como requisito parcial para obtenção do grau de **Engenheiro de Computação**.

**Orientador: Prof. Dr. Mateus Beck Rutzig**

**Santa Maria, RS, Brasil**

**2014**

**Universidade Federal de Santa Maria

Centro de Tecnologia

Curso de Engenharia de Computação**

A Comissão Examinadora, abaixo assinada,

aprova o Trabalho de Conclusão de Curso

**ACOPLAMENTO E VALIDAÇÃO FUNCIONAL DO

SISTEMA RECONFIGURÁVEL DIM**

elaborado por

**Sandro Pedroso Jacobsen**

como requisito parcial para obtenção do grau de

**Engenheiro de Computação**

**COMISSÃO EXAMINADORA:**

---

**Mateus Beck Rutzig, Dr.**

(Presidente/Orientador)

---

**Everton Alceu Carara, Dr. (UFSM)**

(Examinador)

---

**Leonardo Londero de Oliveira, Dr. (UFSM)**

(Examinador)

# **AGRADECIMENTOS**

Agradeço à minha namorada, Tassarine Ferreira Osório, pelo carinho, companheirismo e apoio em todas as etapas da minha jornada acadêmica, estando sempre ao meu lado em todos os momentos.

À minha mãe, Nara Rosane Pedroso Jacobsen, que dedicou muitos anos de sua vida a minha educação, e hoje tenho certeza que está muito feliz por minhas conquistas.

Ao meu pai, José Vamberto Borba Jacobsen, por todo apoio e sacrifícios feitos para que este momento fosse possível.

Ao meu Irmão, Ricky Pedroso Jacobsen, por não medir esforços para me ajudar sempre.

À Simone Lopes Ferreira, pelo apoio e incentivo nessa jornada.

Ao meu amigo e colega Fernando Thiesen Pientka, pelas ajudas fornecidas, conhecimentos compartilhados e momentos de descontração.

Aos demais colegas e amigos, que fizeram esta jornada ser menos árdua, sempre compartilhando momentos de alegria e companheirismo.

Um agradecimento especial ao meu orientador, Mateus Beck Rutzig, pela orientação deste trabalho, apoio e conhecimentos transmitidos durante a graduação.

Aos demais professores do Gmico pelo apoio e colaboração em meu aprendizado.

## **RESUMO**

Trabalho de Conclusão de Curso de Curso

Curso de Engenharia de Computação

Universidade Federal de Santa Maria, RS, Brasil

# **ACOPLAMENTO E VALIDAÇÃO FUNCIONAL DO SISTEMA RECONFIGURÁVEL DIM**

AUTOR: SANDRO PEDROSO JACOBSEN

ORIENTADOR: MATEUS BECK RUTZIG

Local da Defesa e Data: Santa Maria, 11 de Dezembro de 2014.

Arquiteturas Reconfiguráveis vêm sendo largamente exploradas no estado da arte como uma forma de acelerar aplicações embarcadas com eficiência energética, mostrando-se uma alternativa aos processadores superescalares. O sistema DIM é um exemplo de uma arquitetura reconfigurável. Este sistema já se mostra consolidado, pois obtém ganhos significativos em desempenho e energia na execução de aplicações embarcadas. Entretanto, todas as simulações considerando essa arquitetura são realizadas em um alto nível de abstração (Linguagem C++), refletindo uma simulação em nível de instrução. Assim, para uma análise mais acurada dos ganhos pela utilização deste sistema, observou-se a necessidade da verificação de seu funcionamento em nível de precisão de ciclo. Desta forma, obtém-se simulações mais próximas da real execução em hardware, e também é possível estimar o consumo de potência e área. Em vista disso, a proposta deste trabalho é o acoplamento e validação funcional da descrição em VHDL da arquitetura DIM, assim como a obtenção de resultados de potência e área, pós-síntese lógica do sistema. Como contribuição, algumas modificações no código VHDL do sistema foram realizadas para se alcançar a validação funcional do mesmo. Essas modificações ocasionaram um acréscimo de 0,45% no consumo total de potência do sistema, e um acréscimo da área total de 0,25%. Utilizando-se a tecnologia IBM CMOS 7RF ( $0,18 \mu m$ ), obteve-se uma frequência de 150 MHz para o sistema, assim como uma potência total dissipada de 80,217 mW e área total de  $1.925.022 \mu m^2$ .

**Palavras-chave:** Arquitetura Reconfiguráveis; Sistema DIM; Sistemas Embarcados; VHDL;

## **ABSTRACT**

Bachelor's Thesis

Graduation in Computer Engineering

Federal University of Santa Maria, RS, Brazil

## **COUPLING AND VALIDATION OF RECONFIGURABLE SYSTEM DIM**

AUTHOR: SANDRO PEDROSO JACOBSEN

ADVISOR: MATEUS BECK RUTZIG

Place and Date: Santa Maria, December 11<sup>th</sup>, 2014.

Reconfigurable architectures have been widely employed to speedup applications by exploiting instruction level parallelism, appearing as an alternative to replace the power-hungry circuits of superscalar processors. The DIM system is an example of a reconfigurable architecture. This system already shown significant speedups to execute embedded applications. However, the performance results have been gathered by using an instruction accurate description of the architecture. Aiming to gather more accurate performance results and data about power consumption of the DIM system, this work proposes the functional validation of the DIM architecture using an existing VHDL description. As a contribution, some applications were used to validate the existing hardware description. The validated VHDL description presents an overhead of 0.45% in the power consumption and of 0.25% in the area occupied in comparison to the non-validated version.

**Keywords:** Reconfigurable Architecture; DIM System; Embedded System; VHDL;

# ***LISTA DE FIGURAS***

|           |                                                                                                                                                                              |       |       |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|

| Figura 1  | Execução na arquitetura PipeRench - [GOLDSTEIN, 2000]                                                                                                                        | ..... | p. 19 |

| Figura 2  | Organização do sistema DIM.(1)UFR;(2)Processador;(3)TB;(4)Cache de configurações, juntamente com as caches de Instruções e Dados do processador - adaptado de [RUTZIG, 2012] | ..... | p. 21 |

| Figura 3  | Visão geral de uma UFR para máquinas RISC - [BECK FILHO, 2008]                                                                                                               | p. 22 |       |

| Figura 4  | Estrutura de linha de contexto da UFR - [RUTZIG, 2012]                                                                                                                       | ..... | p. 23 |

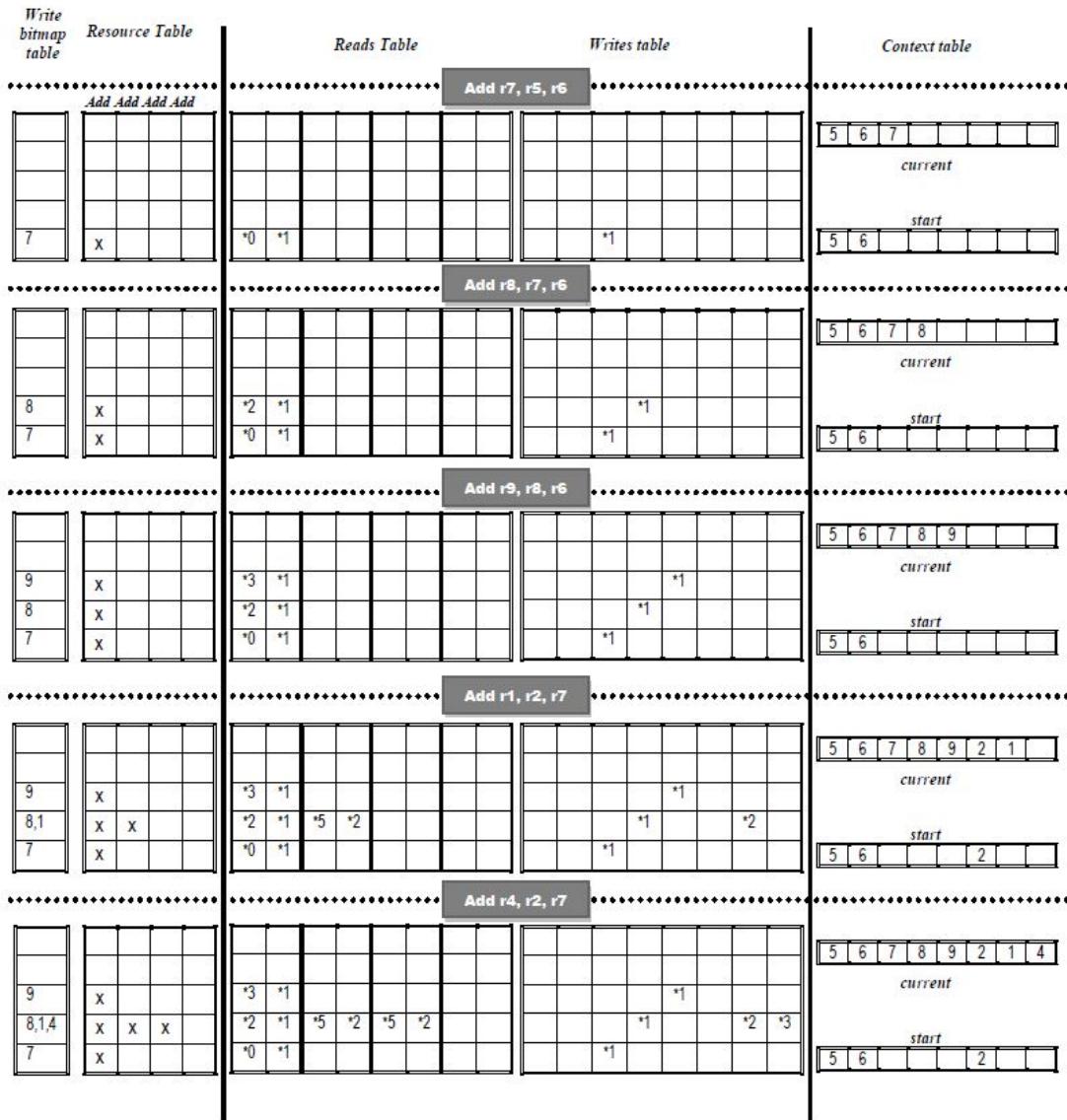

| Figura 5  | Tabelas durante a Detecção de Instruções - [BECK FILHO, 2008]                                                                                                                | ..    | p. 26 |

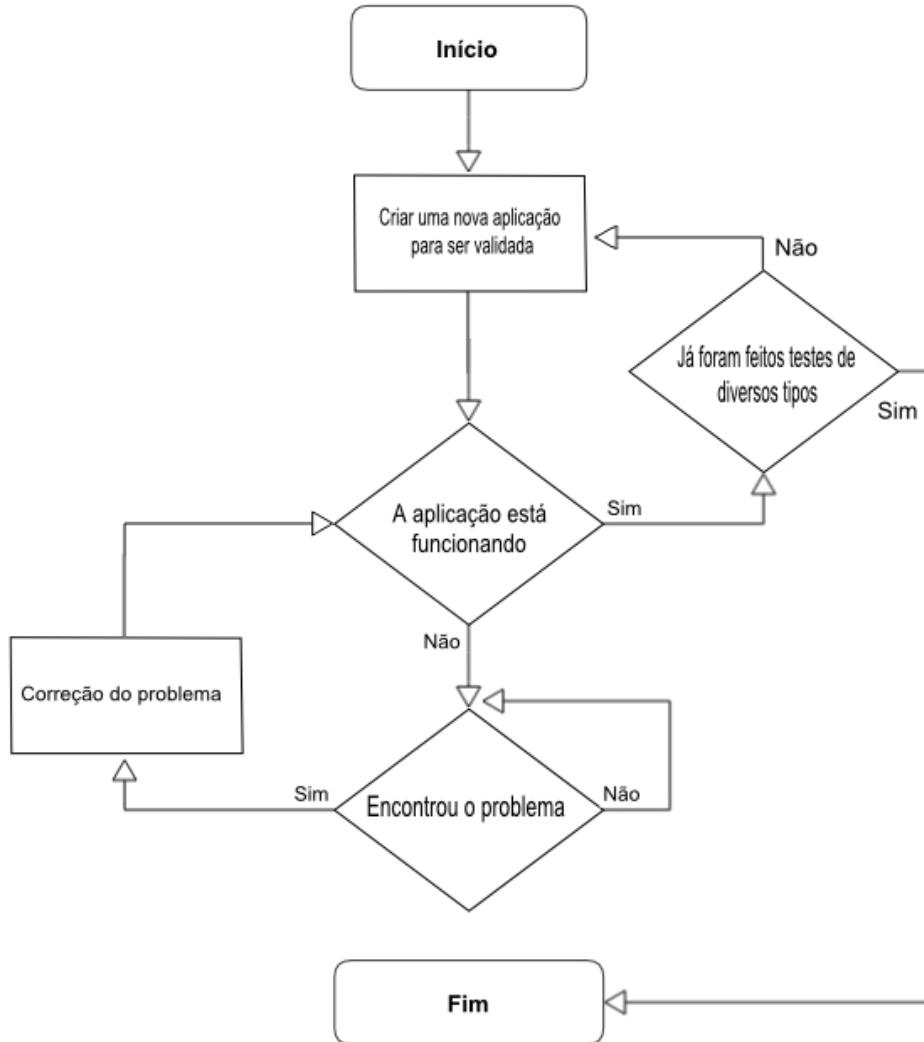

| Figura 6  | Fluxograma mostrando a forma de validação funcional do sistema                                                                                                               | ..    | p. 31 |

| Figura 7  | Aplicação soma de elementos em um loop For                                                                                                                                   | ..... | p. 32 |

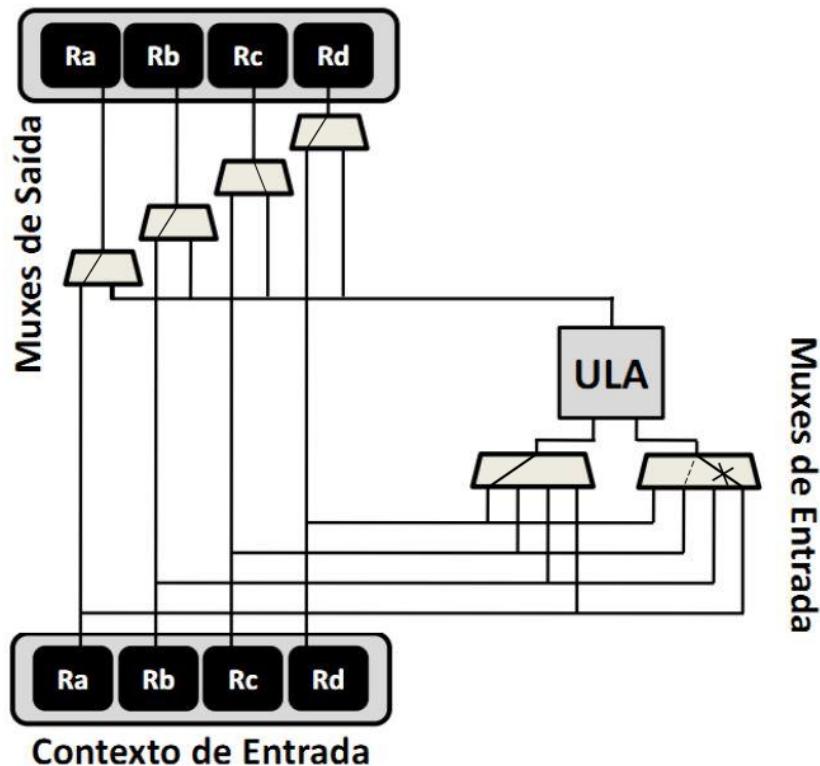

| Figura 8  | Exemplo de seleção incorreta do multiplexador na entrada da ALU da UFR                                                                                                       | ..... | p. 33 |

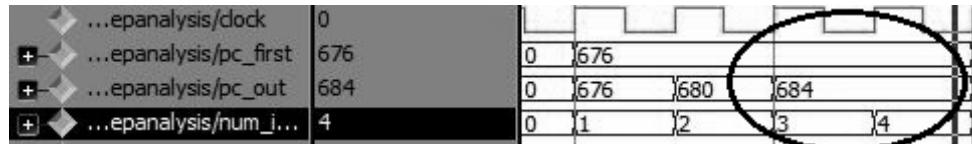

| Figura 9  | Problema no incremento do número de instruções                                                                                                                               | ..... | p. 36 |

| Figura 10 | Aplicação soma de elementos em vários loops For                                                                                                                              | ..... | p. 37 |

| Figura 11 | Simulação com duplicação de configuração na <i>cache</i>                                                                                                                     | ..... | p. 38 |

| Figura 12 | Aplicação de um Bubble Sort                                                                                                                                                  | ..... | p. 39 |

| Figura 13 | Aplicação de soma de matrizes                                                                                                                                                | ..... | p. 41 |

| Figura 14 | Porcentagem de área ocupada por cada módulo do sistema DIM                                                                                                                   | ..    | p. 47 |

| Figura 15 | Porcentagem de potência dissipada por cada módulo do sistema DIM                                                                                                             | p.    | 48    |

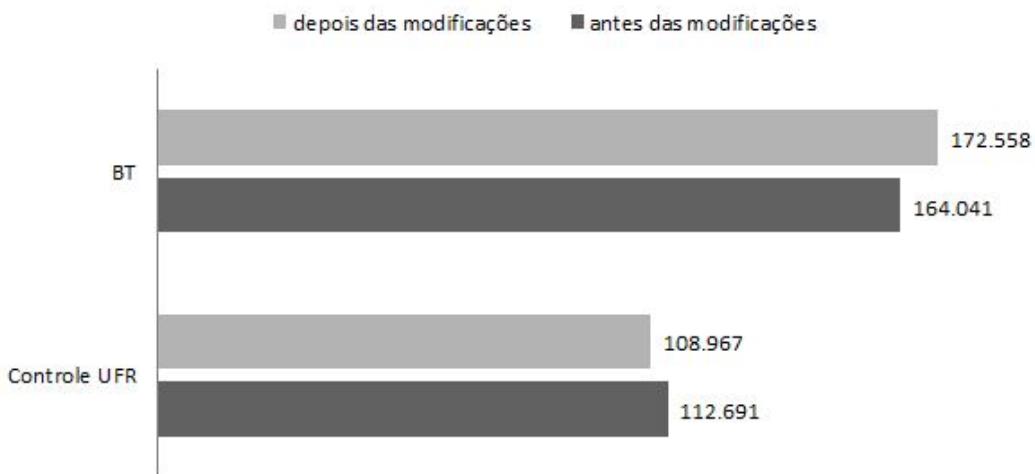

| Figura 16 | Comparação entre a potência (mW) dissipada no TB e controle da UFR em antes e depois das modificações no sistema                                                             | ..... | p. 50 |

| Figura 17 | Comparação entre a área ( $um^2$ ) no TB e controle da UFR antes e depois das modificações no sistema                                                                        | ..... | p. 51 |

| Figura 18 | Modificação feita para atualizar a <i>read_table</i>                                                                                                                         | ..... | p. 57 |

| Figura 19 | Modificação feita para travar o TB quando não modifica o PC                                                                                                                  | ....  | p. 57 |

| Figura 20 | Modificação no último estágio do TB, na criação da configuração                                                                                                              | ..    | p. 58 |

| Figura 21 | Modificação feita na máquina de estados                                                                                                                                      | ..... | p. 58 |

| Figura 22 | Modificação feita no estágio de decodificação do TB                                                                                                                          | ..... | p. 58 |

| Figura 23 | Modificação para que não haja gravação simultânea                                                                                                                            | ..... | p. 58 |

## ***LISTA DE TABELAS***

|          |                                                                              |       |

|----------|------------------------------------------------------------------------------|-------|

| Tabela 1 | Exemplo de <i>Write Bitmap Table</i> (WBT) . . . . .                         | p. 25 |

| Tabela 2 | <i>Context_table_current</i> para a primeira configuração . . . . .          | p. 34 |

| Tabela 3 | <i>Read_table</i> na primeira configuração antes da modificação . . . . .    | p. 34 |

| Tabela 4 | <i>Context_table_current</i> para a segunda configuração . . . . .           | p. 34 |

| Tabela 5 | <i>Read_table</i> para a segunda configuração antes da modificação . . . . . | p. 35 |

| Tabela 6 | <i>Read_table</i> da primeira configuração depois da modificação . . . . .   | p. 35 |

| Tabela 7 | <i>Read_table</i> da segunda configuração depois da modificação . . . . .    | p. 35 |

| Tabela 8 | Características gerais da tecnologia IBM CMOS 7RF [IBM, 2010] . .            | p. 43 |

| Tabela 9 | Potência dos módulos e do Sistema completo em mW . . . . .                   | p. 48 |

# ***LISTA DE ABREVIATURAS***

|       |                                           |

|-------|-------------------------------------------|

| CI    | Circuito Integrado                        |

| DAP   | Dinamic Adapatative Processor             |

| DIM   | Dinamic Instruction Merging               |

| FIFO  | Fist in, Fist Out                         |

| FSM   | Finite State Machine                      |

| ILP   | Instruction-Level Parallelism             |

| ISA   | Instruction Set Architecture              |

| PC    | Program Counter                           |

| PPG   | Processador de Propósito Geral            |

| RAW   | Read After Write                          |

| RBT   | Read Bitmap Table                         |

| TLP   | Thread-Level Parallelism                  |

| TB    | Tradutor Binário                          |

| UFR   | Unidade Funcional Reconfiguravel          |

| ULA   | Unidade Lógica e Aritmética               |

| UFSM  | Universidade Federal de Santa Maria       |

| UFRGS | Universidade Federal do Rio Grande do Sul |

| VHDL  | VHSIC Hardware Description Language       |

| VLIW  | Very Long Instruction Word                |

| WAR   | Write After Read                          |

| WAW   | Write After Write                         |

| WBT   | Write Bitmap Table                        |

# **SUMÁRIO**

## **Agradecimentos**

## **Resumo**

## **Abstract**

|          |                                                                  |       |

|----------|------------------------------------------------------------------|-------|

| <b>1</b> | <b>Introdução</b>                                                | p. 13 |

| <b>2</b> | <b>Trabalhos Relacionados</b>                                    | p. 16 |

| 2.1      | Classificação . . . . .                                          | p. 16 |

| 2.1.1    | Acoplamento . . . . .                                            | p. 16 |

| 2.1.2    | Granularidade . . . . .                                          | p. 17 |

| 2.1.3    | Mecanismo de Reconfiguração . . . . .                            | p. 17 |

| 2.2      | Exemplos de Abordagens de Arquiteturas Reconfiguráveis . . . . . | p. 18 |

| 2.2.1    | Chimaera . . . . .                                               | p. 18 |

| 2.2.2    | PipeRench . . . . .                                              | p. 18 |

| 2.2.3    | TRIPS . . . . .                                                  | p. 19 |

| 2.2.4    | <i>Warp Processor</i> . . . . .                                  | p. 20 |

| 2.2.5    | DIM . . . . .                                                    | p. 20 |

| <b>3</b> | <b>Sistema Reconfigurável DIM</b>                                | p. 21 |

| 3.1      | Processador . . . . .                                            | p. 22 |

| 3.2      | Unidade Funcional Reconfigurável . . . . .                       | p. 22 |

| 3.3      | Tradutor Binário . . . . .                                       | p. 23 |

|          |                                                                       |       |

|----------|-----------------------------------------------------------------------|-------|

| 3.3.1    | Tabelas Utilizadas nas Configurações . . . . .                        | p. 24 |

| 3.3.1.1  | Exemplo de Funcionamento das Tabelas . . . . .                        | p. 25 |

| 3.3.2    | Algoritmo de Tradução Binária . . . . .                               | p. 27 |

| 3.4      | <i>Cache</i> de Configurações . . . . .                               | p. 28 |

| 3.5      | Funcionamento do Sistema . . . . .                                    | p. 29 |

| <b>4</b> | <b>Acoplamento e Validação do Sistema DIM</b>                         | p. 30 |

| 4.1      | Histórico de implementação . . . . .                                  | p. 30 |

| 4.2      | Metodologia de Acoplamento e Validação Funcional do Sistema . . . . . | p. 31 |

| 4.3      | Aplicação de soma de elementos em um loop For . . . . .               | p. 32 |

| 4.3.1    | Atualização da <i>Read table</i> . . . . .                            | p. 33 |

| 4.3.2    | Problema no incremento do número de instruções . . . . .              | p. 35 |

| 4.4      | Aplicação de soma de elementos em vários loops For . . . . .          | p. 37 |

| 4.4.1    | Gravação duplicada de uma configuração . . . . .                      | p. 38 |

| 4.5      | Aplicação <i>Bubble Sort</i> . . . . .                                | p. 38 |

| 4.5.1    | Busca na <i>cache</i> de configurações com PC incorreto . . . . .     | p. 39 |

| 4.5.2    | Continuação de uma configuração mesmo após execução na UFR .          | p. 40 |

| 4.5.3    | Configurações criadas na inicialização do programa . . . . .          | p. 40 |

| 4.6      | Soma de Matrizes . . . . .                                            | p. 41 |

| 4.6.1    | Registrador com dado inconsistente . . . . .                          | p. 41 |

| <b>5</b> | <b>Resultados</b>                                                     | p. 43 |

| 5.1      | Metodologia . . . . .                                                 | p. 43 |

| 5.2      | Análises dos Resultados . . . . .                                     | p. 45 |

| 5.2.1    | Desempenho . . . . .                                                  | p. 46 |

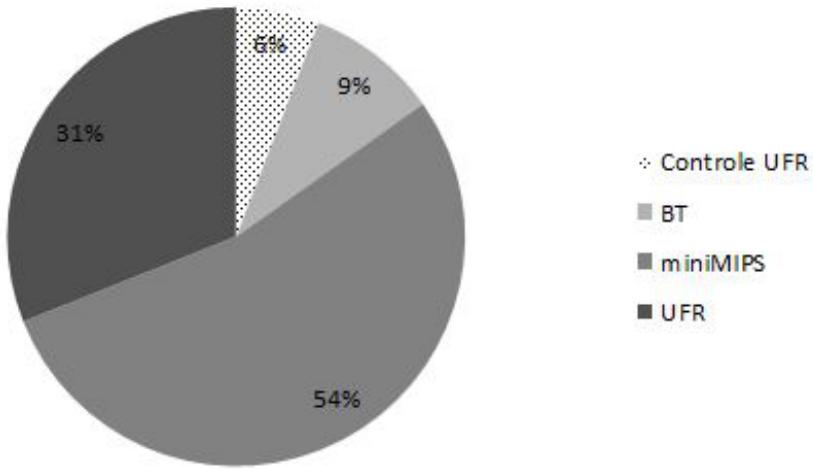

| 5.2.2    | Área . . . . .                                                        | p. 46 |

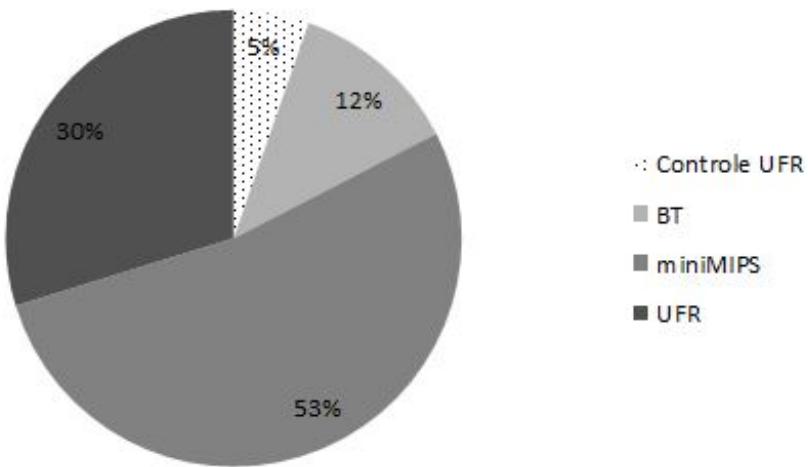

| 5.2.3    | Potência . . . . .                                                    | p. 47 |

| 5.2.4    | Caminho Crítico . . . . .                                             | p. 48 |

## *Sumário*

---

|                                         |                                                                                                 |       |

|-----------------------------------------|-------------------------------------------------------------------------------------------------|-------|

| 5.2.5                                   | Energia . . . . .                                                                               | p. 49 |

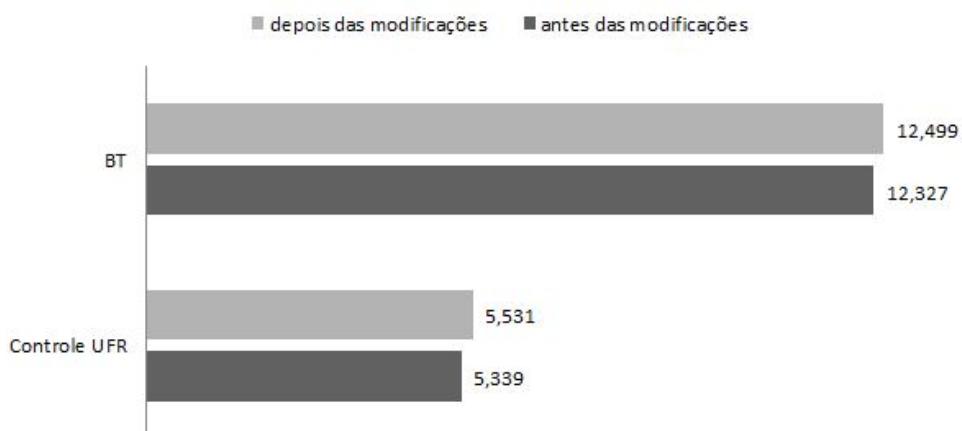

| 5.3                                     | Análises do Efeito das Modificações em Potência, Área e Caminho Crítico<br>do Sistema . . . . . | p. 49 |

| 5.3.1                                   | Potência . . . . .                                                                              | p. 50 |

| 5.3.2                                   | Área . . . . .                                                                                  | p. 50 |

| 5.3.3                                   | Caminho Crítico . . . . .                                                                       | p. 51 |

| <b>6</b>                                | <b>Considerações Finais e Trabalhos Futuros</b>                                                 | p. 52 |

| 6.1                                     | Trabalhos Futuros . . . . .                                                                     | p. 52 |

| 6.1.1                                   | Aumento da Unidade Funcional Reconfigurável . . . . .                                           | p. 53 |

| 6.1.2                                   | Otimização da Unidade Funcional Reconfigurável . . . . .                                        | p. 53 |

| 6.1.3                                   | Otimização do Bloco de Dependência de Dados do TB . . . . .                                     | p. 53 |

| 6.1.4                                   | Otimização da Inicialização de uma Execução na UFR . . . . .                                    | p. 53 |

| 6.1.5                                   | Síntese Física do Sistema DIM . . . . .                                                         | p. 54 |

| 6.1.6                                   | Verificação do Impacto Causado pela Inserção de uma NoC em<br>Vários Cores do Sistema . . . . . | p. 54 |

| <b>Referências</b>                      |                                                                                                 | p. 55 |

| <b>Apêndice A – Códigos Modificados</b> |                                                                                                 | p. 57 |

# 1 INTRODUÇÃO

Com o aumento no número de aplicações embarcadas, a estratégia atual das grandes empresas do mercado é disponibilizar plataformas embarcadas que provêm a execução eficiente destas aplicações em relação ao consumo de energia e desempenho. Para atingir estes objetivos, muitas abordagens utilizam processadores superescalares. Estes processadores exploram o paralelismo em nível de instrução (ILP) de maneira a disponibilizar a execução de mais de uma instrução por ciclo de clock. Entretanto, há três fatores limitantes de desempenho para este tipo de arquitetura: Dependência verdadeira de dados, dependência de desvios e dependência de recursos. A dependência verdadeira ocorre quando uma instrução depende dos dados produzidos por uma instrução anterior a ela. Desta forma, a instrução seguinte somente poderá iniciar a sua execução após o término da instrução anterior. Dependência de desvios ocorre devido a os desvios condicionais, a execução das instruções seguintes ao desvio somente poderá acontecer após a decisão do desvio. Já a dependência de recursos ocorre quando duas ou mais instruções competem, ao mesmo tempo, por um recurso, como por exemplo, barramento, unidade lógica e aritmética (ULA), memória *cache*, entre outros. Devido a essas dependências, o desempenho dos processadores superescalares atuais não segue a Lei de Moore.

Uma das alternativas as arquiteturas superescalares é a arquitetura VLIW (Very Long Instruction Word). Esta arquitetura também explora o paralelismo em nível de instrução, este paralelismo é extraído em tempo de compilação. Desta forma, não é necessária a utilização de hardware dedicado para tal tarefa, por conseguinte, estas arquiteturas mostram-se eficientes do ponto de vista energético [HENNESSY; PATTERSON, 2012]. No entanto, faz-se necessário a existência de um compilador específico para a alocação eficiente das instruções a serem executadas, necessitando portanto, recompilação de códigos já existentes para que seja possível executá-los neste tipo de arquitetura. Em vista disso, há uma dificuldade na adoção das arquiteturas VLIW, pois no mercado de sistemas embarcados a compatibilidade binária é um fator decisivo devido ao *time-to-market*.

Arquiteturas reconfiguráveis aparecem como uma solução viável para atingir os obje-

tivos do mercado atual de sistemas embarcados. Estas arquiteturas vêm demonstrando ganhos de desempenho significativos, conforme vistos em [GUPTA, 1993] e [GAJSKI, 1998]. Com redução significativa do tempo de execução, arquiteturas reconfiguráveis também se tornam eficiente em termos de energia como pode ser visualizado em [WAN, 1998] e [STITT, 2002], algo extremamente desejável em sistemas embarcados. Entretanto, um dos grandes empecilhos para a adoção de arquiteturas reconfiguráveis é a necessidade de utilização de novas plataformas de desenvolvimento de software. Novas ferramentas são criadas, ocasionando assim a mesma quebra da compatibilidade binária provida pelos processadores VLIW, o que é extremamente indesejável.

Entretanto, o emprego de reconfiguração dinâmica do sistema reconfigurável evita a perda da compatibilidade binária, visto que ao mesmo tempo em que a aplicação é executada no processador, existe um bloco que analisa as instruções em execução e as transforma em configurações da unidade funcional reconfigurável (UFR). Assim, na segunda execução deste determinado trecho de código, a UFR é configurada para executá-lo.

Pensando nisso, desenvolveu-se no laboratório de sistemas embarcados da Universidade Federal do Rio Grande do Sul (UFRGS) uma arquitetura reconfigurável que realiza a detecção de instruções executadas pelo processador de propósito geral e as traduz em configurações da arquitetura reconfigurável em tempo de execução. Desta forma, acelera-se a aplicação e mantém-se a compatibilidade binária. Este sistema foi chamado de DIM (*Dynamic Instruction Merging*) e seu funcionamento foi proposto em [BECK FILHO, 2008]. Atualmente, o sistema DIM está modelado em um simulador descrito em um alto nível de abstração (linguagem C++) que provê uma simulação em nível de precisão de instrução. Resultados obtidos a partir deste simulador demonstram que, em média, para 12 aplicações executadas, a arquitetura reconfigurável proposta obtém 2,7 vezes de aceleração em relação a um processador *pipeline* surgindo como uma nova alternativa para aceleração de aplicações embarcadas. Entretanto, a simulação em um alto nível de abstração provê alguns empecilhos como: baixa precisão dos resultados de simulação e a impossibilidade de estimar a potência consumida e frequência do circuito.

Os empecilhos descritos anteriormente acabam por motivar a proposta deste trabalho. Alguns trabalhos [LAZZAROTTO, 2011], [GEGLER, 2007] e [NAZAR, 2008] já propuseram a descrição isolada dos blocos da arquitetura DIM em VHDL no Laboratório de Sistemas Embarcados da UFRGS. Entretanto, como estes blocos não foram integrados, ou seja, a validação funcional e a extração de resultados do sistema completo não foram realizados.

Para este trabalho é proposto o acoplamento e validação funcional destes blocos em um sistema integrado possibilitando assim a simulação da arquitetura em nível de precisão de ciclo e a extração de resultados de consumo de potência, área e frequência de operação a partir da síntese lógica em uma tecnologia CMOS.

O Capítulo 2 apresenta algumas classificações que circundam arquiteturas reconfiguráveis e os trabalhos relacionados semelhantes ao utilizado nesta proposta. O sistema DIM, arquitetura utilizada neste trabalho, é apresentado de forma mais detalhada no Capítulo 3. A metodologia, as aplicações utilizadas para validar funcionalmente o sistema e as modificações necessárias no código do sistema são mostradas no Capítulo 4. O Capítulo 5 apresenta os resultados obtidos do sistema, como consumo de potência, desempenho e área a partir da síntese lógica do sistema DIM em VHDL. O Capítulo 6 possui as considerações finais e trabalhos futuros.

## **2 TRABALHOS RELACIONADOS**

Neste capítulo serão demonstradas algumas classificações em torno de arquiteturas reconfiguráveis, também serão demonstrados alguns trabalhos propostos sobre este tema.

### **2.1 Classificação**

Ainda não existe um consenso para classificar as arquiteturas reconfiguráveis. Assim, a classificação apresentada é baseada em [COMPTON, 2002], sendo distinguidas em três aspectos: Acoplamento, Granularidade e Mecanismo de Reconfiguração.

#### **2.1.1 Acoplamento**

O acoplamento se refere à distância entre o processador e a unidade funcional reconfigurável (UFR), refletindo diretamente na eficiência do sistema reconfigurável. Uma unidade funcional reconfigurável implementada dentro do processador é chamada de fortemente acoplada, sendo a comunicação entre eles realizada dentro do núcleo o que evita perdas de desempenho devido a comunicação. Porém, quando não há área de silício suficiente para inserir a UFR dentro do processador é necessário tratá-la como um co-processador. Desta forma, a comunicação tem de ser feita por um barramento externo, acarretando em um tempo mais alto de comunicação que a abordagem anterior.

Existem outras técnicas de acoplamento chamadas de fracamente acopladas e abordagem de acoplamento independente. A primeira tem um alto custo de comunicação, visto que a UFR é anexada e fica localizada no barramento que conecta a memória *cache* e a interface de entrada/saída. Já a abordagem de acoplamento independente possui um custo de comunicação ainda maior, pois se comunica somente pelo barramento de entrada/saída, sendo portanto a abordagem que é mais fracamente acoplada.

### 2.1.2 Granularidade

A unidade funcional reconfigurável pode ser implementada através de diferentes tipos e tamanhos de blocos funcionais, isto é o que determina sua granularidade. Por exemplo, uma unidade reconfigurável pode utilizar a replicação de somadores de 32 bits, ou também, podem-se utilizar somadores independentes de um bit para realizar uma soma.

De acordo com a granularidade escolhida para a UFR, há uma influência direta no número de bits necessários para realizar uma configuração. Somando ao exemplo anterior, verifica-se que ao utilizar um somador de 32 bits o controle para realizar esta operação é bastante simplificado, já para realizar a mesma soma com somadores independentes de um bit seria necessário um elevado número de bits para controlar essa soma, aumentando consideravelmente a complexidade da operação. Uma abordagem de grão grosso, caso do somador de 32 bits, tem o ganho na simplicidade e menor número de bits de configuração. Já a abordagem de grão fino, somadores de um bit, é mais diversificada podendo realizar diferentes operações, porém tem um controle muito complexo e necessita de muitos bits para configurar a sua correta execução.

### 2.1.3 Mecanismo de Reconfiguração

O mecanismo utilizado para reconfiguração da UFR é muito importante para a eficiência do sistema. Em [HUTCHINGS, 1999] foi demonstrado um mecanismo que, em tempo de compilação, extrai partes do programa que podem ser executadas de forma eficiente na unidade funcional reconfigurável. Porém, técnicas como esta são feitas em tempo de compilação e, portanto, necessita de recompilação de todo código para utilizar a UFR. Isto acarreta em um elevado tempo de projeto, não provendo compatibilidade binária com códigos feitos anteriormente a adoção desta técnica.

Outra técnica utilizada é a detecção de partes da aplicação que podem ser alocadas na UFR em tempo de execução, ou seja, enquanto o processador está executando são criadas configurações que executarão na UFR em uma próxima execução do mesmo trecho de código. Um dos pioneiros a utilizar esta técnica é [LYSECKY, 2006] que verifica e cria uma reconfiguração em tempo de execução. Esta abordagem é mais complexa que a anterior, porém trás uma redução no tempo de desenvolvimento, pois mantém a compatibilidade binária com códigos descritos antes da utilização desta técnica, não havendo necessidade de recompilação destes códigos.

## 2.2 Exemplos de Abordagens de Arquiteturas Reconfiguráveis

Esta seção irá mostrar algumas propostas que utilizam arquiteturas reconfiguráveis. Também serão analisadas algumas vantagens e desvantagens destas arquiteturas comparadas com a arquitetura utilizada neste trabalho.

### 2.2.1 Chimaera

Chimaera é um sistema que possui característica de ser fortemente acoplado ao processador, compartilhando recursos como o banco de registradores [HAUCK, 1997]. Este sistema foi projetado para suportar computações intensivas em um FPGA. O bloco lógico da UFR pode ser configurado como 4-LUT, duas 3-LUTs ou uma 3-LUT, com computação de *carry*. Este sistema possui instruções específicas para executar uma função na UFR, sendo usadas técnicas de reconfiguração parcial em tempo de execução para gerenciar o FPGA.

Para utilizar a unidade funcional reconfigurável são necessárias ferramentas auxiliares específicas para esta tecnologia, como compilador e ferramentas de CAD - Mapeamento, posicionamento e roteamento. Portanto, o sistema Chimaera consiste basicamente de uma UFR fortemente acoplada ao processador, tornando mais rápida a comunicação e aumentando o desempenho do processador. Em contrapartida não apresenta compatibilidade binária, necessitando de um compilador próprio e algumas ferramentas de CAD.

### 2.2.2 PipeRench

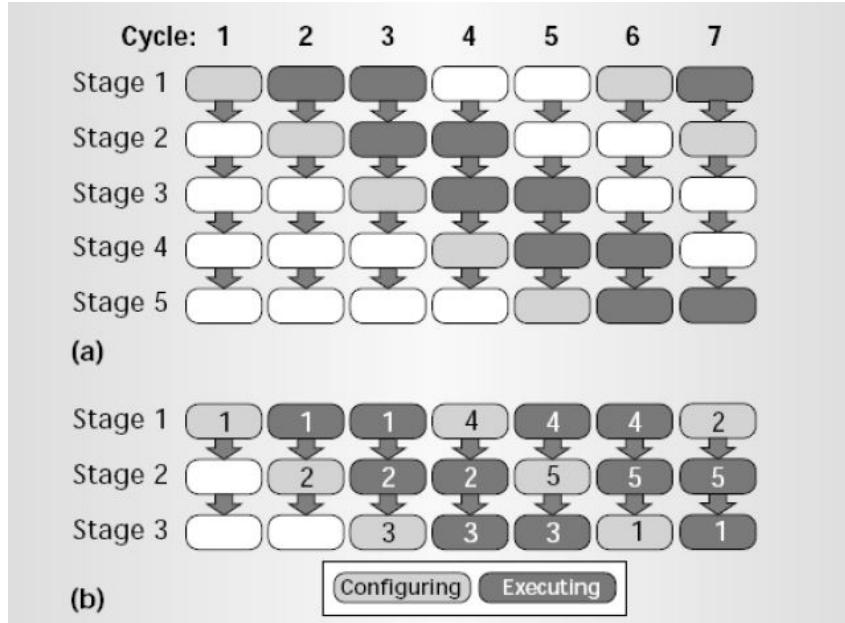

[GOLDSTEIN, 2000] mostra uma proposta de computação reconfigurável que utiliza *pipeline* para aumentar o desempenho de configuração e execução em um FPGA. Uma demonstração do funcionamento desta técnica é mostrado na Figura 1. Nesta Figura é ilustrada a execução de uma aplicação que foi dividida em 5 estágios de *pipeline* (Figura 1(a)) levando 7 ciclos para ser configurada e executada. Já a Figura 1(b) mostra a aplicação da técnica de virtualização nesta aplicação, sendo assim executada em 3 ciclos somente.

PipeRench propõe um acoplamento da unidade funcional reconfigurável com o processador, ou seja, utiliza a abordagem fortemente acoplada. No entanto também precisa de um compilador específico para otimização do código utilizando a técnica de virtualização

e não provê compatibilidade binária.

Figura 1: Execução na arquitetura PipeRench - [GOLDSTEIN, 2000]

### 2.2.3 TRIPS

A arquitetura TRIPS [SANKARALINGAM, 2004] mostra grande eficiência para aplicações com alto paralelismo em nível de instrução (ILP), pois tem núcleos grandes e granularidade do tipo grão-grosso. No entanto, o sistema também pode ser configurado para aplicações com alto paralelismo em nível de *thread* (TLP) obtendo bons níveis de acelerações.

O TRIPS *chip* é composto de um banco de memória e TRIPS *cores*, sendo que cada *core* contém *cache* de dados e de instruções, banco de registradores e uma matriz homogênea de nós processantes, cada um contendo uma ALU, uma unidade de ponto flutuante, um conjunto de estações de reserva e conexões de roteamento na entrada e saída.

O objetivo deste sistema é obter um desempenho semelhante ao de sistemas de propósito específico, como por exemplo, processadores gráficos, DSPs, evitando assim a necessidade de um sistema heterogêneo. Os resultados obtidos na aceleração de aplicações pela utilização desta arquitetura são satisfatórios, porém há uma necessidade de um *toolchain* específico, visto que este sistema possui uma ISA (*Instruction Set Architecture*) própria, não provendo compatibilidade de software.

### 2.2.4 Warp Processor

O sistema Warp é descrito em [LYSECKY, 2006], sendo um sistema que utiliza um microprocessador, um módulo FPGA, uma unidade de *profiling* de software e um módulo CAD. Seu funcionamento básico consiste em identificar (via *profiling*) as regiões críticas de um código binário e traduzi-las dinamicamente em circuitos mapeáveis em FPGA. Esta tradução é feita pelo módulo CAD. Após a tradução ocorre uma modificação no binário para que na próxima execução desta região crítica seja realizada no FPGA.

A arquitetura Warp não necessita de compiladores especiais, pois o código é analisado em tempo de execução. Essa característica difere dos sistemas vistos anteriormente e, portanto, provê compatibilidade binária com códigos anteriores. A desvantagem desse sistema é que a aceleração só ocorre em aplicações passíveis de aceleração utilizando FPGA em que a região crítica da aplicação não possui aritmética de ponto flutuante, alocação dinâmica de memória, recursão ou ponteiros.

### 2.2.5 DIM

O sistema DIM [BECK FILHO, 2008], a arquitetura utilizada neste trabalho, é um sistema reconfigurável dinâmico, assim mantendo a compatibilidade de software com software legado. A arquitetura analisa as instruções que estão sendo executadas no processador de propósito geral (PPG) e cria configurações paralelamente à execução destas instruções, salvando-as em uma *cache* de configurações. Desta forma, a próxima execução deste trecho de código se dará, de forma totalmente combinacional, na unidade funcional reconfigurável ao invés de se dar no PPG. Assim, além dos ganhos da execução totalmente combinacional, o paralelismo em nível de instrução é explorado, aumentando o desempenho da aplicação. Mais detalhes sobre o Sistema DIM serão demonstrados no capítulo 3.

# **3 SISTEMA RECONFIGURÁVEL DIM**

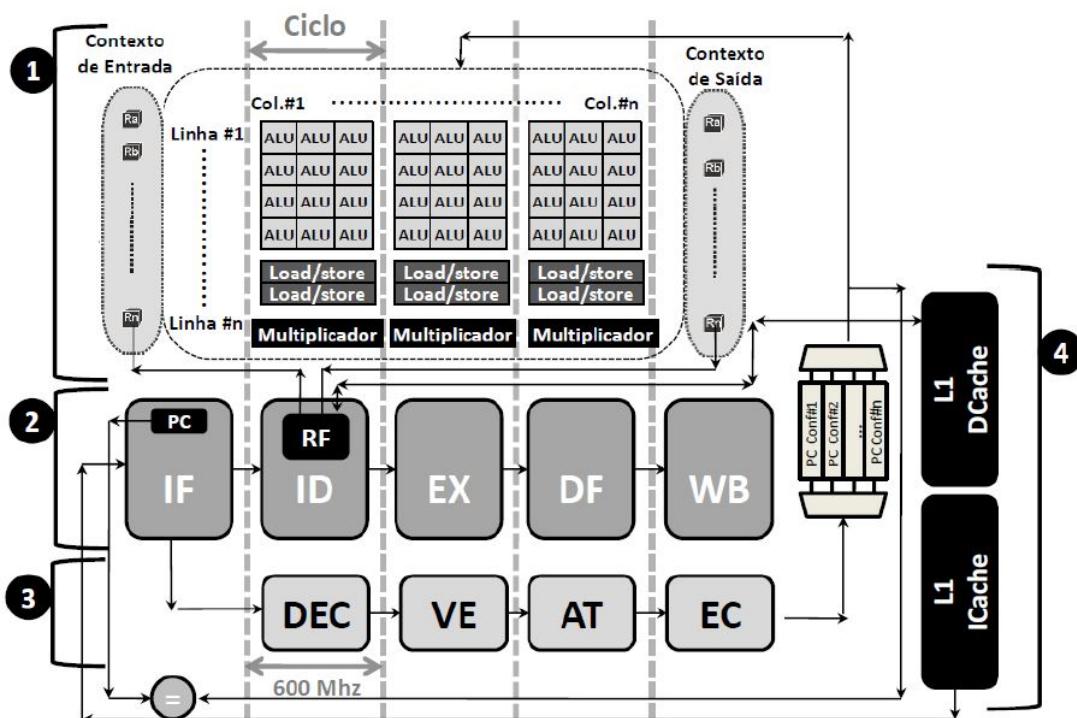

Como já explicitado anteriormente, o objetivo deste trabalho é realizar o acoplamento e validação do sistema DIM (*Dinamic Instruction Merging*), descrito em [BECK FILHO, 2008] e desenvolvido no laboratório de Sistemas Embarcados do Instituto de Informática da UFRGS. O sistema baseia-se no conceito de arquiteturas reconfiguráveis, possibilitando a exploração de um alto paralelismo em nível de instrução (ILP). Outro ponto importante desta arquitetura é o fato de manter a compatibilidade binária com ISAs existentes. O sistema é composto de: um processador de propósito geral, uma unidade funcional reconfigurável (UFR), um tradutor binário (BT), uma cache de configurações e um controle para carregar as configurações que serão executadas na UFR. Os componentes do sistema podem ser visto na Figura 2.

Figura 2: Organização do sistema DIM.(1)UFR;(2)Processador;(3)TB;(4)Cache de configurações, juntamente com as caches de Instruções e Dados do processador - adaptado de [RUTZIG, 2012]

### 3.1 Processador

O sistema pode funcionar com diversas ISAs, precisando de apenas algumas modificações para utilização de um ou outro processador de propósito geral. Neste trabalho foi utilizado o processador miniMIPS [MINIMIPS, 2008], uma implementação aberta em VHDL do processador MIPS R3000, que utiliza a ISA MIPS I. Este processador possui um pipeline de cinco estágios [MINIMIPS, 2008].

### 3.2 Unidade Funcional Reconfigurável

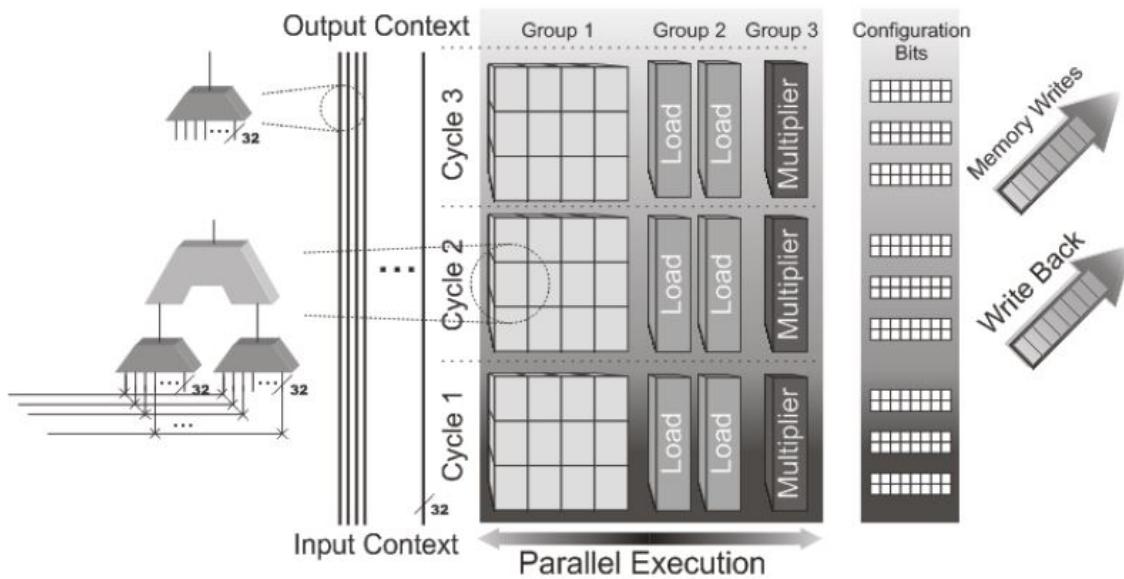

Uma abordagem geral de funcionamento de uma unidade funcional reconfigurável pode ser vista na Figura 3, sendo basicamente uma matriz com várias unidades funcionais que podem executar em paralelo obtendo assim um alto ILP.

Figura 3: Visão geral de uma UFR para máquinas RISC - [BECK FILHO, 2008]

A unidade reconfigurável é dividida em ciclos, cada ciclo possui o tempo de um acesso à memória. Nesta implementação, é possível realizar a computação de duas operações de ALUs com dependência de dados em um ciclo de relógio. Entretanto, o número de ALUs em série depende diretamente do tempo de acesso à memória que é seu caminho crítico.

O contexto de entrada da unidade reconfigurável contém os valores dos registradores e imediatos que serão utilizados na execução de uma configuração. Os dados dos registradores são buscados do banco de registradores do processador, onde serão salvos após a execução na UFR. Já os valores imediatos são carregados a partir da configuração

armazenada na *cache*.

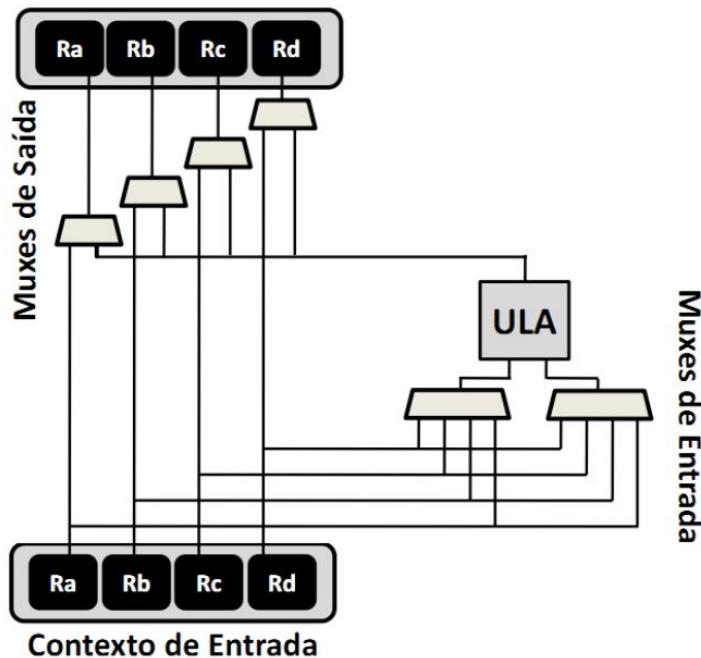

Após o carregamento do contexto de entrada, a computação é realizada de forma combinacional em todas as unidades funcionais. O funcionamento da carga do contexto de entrada para uma ALU e o salvamento do contexto de saída da mesma pode ser visualizado na Figura 4.

Figura 4: Estrutura de linha de contexto da UFR - [RUTZIG, 2012]

Basicamente, na entrada da ALU chega todo o contexto de entrada do ciclo, sendo selecionada a entrada por um multiplexador que é controlado pelos bits de configuração armazenados na *cache*. O contexto de saída funciona de forma similar, podendo ser salvo o valor do contexto de entrada, caso não haja gravação no respectivo registrador, ou o dado calculado pela ALU. A escolha é feita através de um multiplexador que também é controlado pelos bits de configuração armazenados na *cache*, que haviam sido salvos pelo tradutor binário.

### 3.3 Tradutor Binário

O tradutor binário é o módulo que cria as configurações que serão executadas na unidade funcional reconfigurável. Este bloco decodifica as instruções que estão executando no processador, verifica as dependências entre elas, aloca recursos da UFR de forma correta e cria configurações que serão salvas na *cache* de configurações.

A Figura 2(3) mostra os quatro estágios de *pipeline* do TB. Como pode ser visto o tradutor binário executa em paralelo ao processador, então é necessário garantir que os estágios do TB não terão tempos de execução superiores ao do processador, pois isso ocasionaria uma necessidade de redução da frequência de funcionamento do processador.

### 3.3.1 Tabelas Utilizadas nas Configurações

Existem algumas tabelas em que o Tradutor Binário se baseia para construir as configurações que serão armazenadas na *cache*. A nomenclatura mostrada a seguir é a mesma vista em [BECK FILHO, 2008].

- *Write Bitmap Table*: Indica quais registradores serão escritos. Há um bit para cada registrador utilizado e uma linha para cada linha da UFR. Se o bit é setado com o valor um, indica que o registrador é gravado naquela linha, caso contrário não. Esta tabela é utilizada para verificações de dependência *Read After Write* (RAW) e *Write After Write* (WAW). A Tabela 1 mostra um exemplo de *Write Bitmap Table* em uma UFR com 4 linhas e 16 registradores.

- *Resource Table*: É utilizado um bit para indicar se o recurso (ULA, Load/Store, Multiplicador) da UFR está sendo usado. Há uma *Resource Table* para cada grupo de unidades, sendo que a *Resource Table* para ULAs pode ser vista no exemplo mostrado na Figura 5.

- *Read Table*: Indica quais registradores serão lidos pela UFR. Esta tabela é quem controla os multiplexadores que serão lidos nas unidades funcionais. Estes registradores têm por base os utilizados na *Current Table*, ou seja, é armazenado um ponteiro para o valor que há na tabela. O exemplo da Figura 5 mostra o funcionamento da *Read Table*.

- *Write Table*: Informa onde será gravada a operação, ou seja, controla os multiplexadores de saída. Caso o valor do contexto de entrada seja mantido, caso em que não há gravação no registrador, o valor da *Write Table* para este registrador é zero. A Figura 5 mostra o funcionamento da *Write Table*, considerando que onde não há valor algum este é zero, para passar o dado que havia no contexto de entrada.

- *Context Table*: Esta tabela contém os registradores de contexto e os operandos imediatos que serão executados na UFR. Esta tabela subdivide-se em três, a *Current Table*, *Start Table* e *Immediate Table*. A Figura 5 mostra o funcionamento da

*Context Table* e da *Start Table*, com exceção da *Immediate Table* pois não é utilizado nenhum valor imediato no exemplo, mas esta tabela segue a mesma forma da *Current Table*.

- *Current Table*: Possui os registradores que serão utilizados na atual configuração. No entanto possui o endereço do registrador utilizado, não o valor contido nele. Representa o estado final que será escrito no processador quando a UFR terminar de executar.

- *Start Table*: Indica os registradores que serão lidos inicialmente na UFR, indicando o contexto de entrada da *Current Table*. Esta tabela é usada para buscar os operandos de entrada na fase de reconfiguração.

- *Immediate Table*: Esta tabela contém os valores imediatos que serão utilizados durante a execução na UFR, armazenando o valor imediato direto na configuração.

- *Function Table*: Informa qual a função que será executada na unidade funcional, pois existem diversas operações que podem ser executadas em uma UFR.

- *Read Bitmap Table*: Similar a *Write Bitmap Table*, esta tabela indica se o registrador é lido em alguma operação na linha da UFR. É utilizada para analisar dependências do tipo *Write After Read* (WAR).

Tabela 1: Exemplo de *Write Bitmap Table*(WBT)

| Registradores |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    | Linhas  |

|---------------|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|---------|

| r15           | r14 | r13 | r12 | r11 | r10 | r9 | r8 | r7 | r6 | r5 | r4 | r3 | r2 | r1 | r0 |         |

| 0             | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | Linha 4 |

| 0             | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 0  | Linha 3 |

| 0             | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | 0  | Linha 2 |

| 0             | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | Linha 1 |

### 3.3.1.1 Exemplo de Funcionamento das Tabelas

Para entender melhor o funcionamento das tabelas é mostrado na Figura 5 um exemplo simples visto em [BECK FILHO, 2008], com apenas operações de adição, mostrando algumas dependências de dados e como são alocadas as tabelas nesses casos.

O código executado é:

Figura 5: Tabelas durante a Detecção de Instruções - [BECK FILHO, 2008]

```

add r7,r5,r6

add r8,r7,r6

add r9,r8,r6

add r1,r2,r7

add r4,r3,r7

```

Como pode ser visto na Figura 5, os recursos são alocados de acordo com as dependências de dados das instruções. Ao executar a instrução add r7,r5,r6 no processador, o tradutor binário começa uma nova configuração. É inserido na *Write bitmap table* o endereço do registrador r7 que indica o registrador que será gravado o valor da operação. A *Resource Table* aloca uma unidade para a execução da instrução, neste caso uma ALU. A *Reads Table* armazena um ponteiro para o endereço armazenado na *current table*, indi-

cando os registradores de leitura na execução da instrução. Na *Writes table* armazena-se um ponteiro para o endereço armazenado na *Write bitmap table*, indicando o registrador que será gravado e a unidade funcional que está sendo alocada para ele. Este ponteiro é armazenado na mesma posição onde o registrador que será gravado encontra-se na *current table*. Na *current table* são armazenados todos os registradores que serão utilizados na operação, nesta instrução r5, r6 e r7. Por fim a *start table* irá conter todos os registradores que serão carregados diretamente do contexto de entrada para as unidades funcionais, inicializando com os registradores r5 e r6.

A segunda instrução (add r8,r7,r6) é alocada em série à primeira, visto que possui uma dependência de dados do tipo *Read After Write* (RAW). Desta forma, insere-se na *Write bitmap table* o registrador r8 que será gravado o dado computado. A *Resource table* é atualizada de acordo com a dependência do registrador r7. É inserido na *Reads table*, os ponteiros para os endereços, armazenados na *current table*, dos registradores de entrada. Estes ponteiros são inseridos na posição da ALU alocada. A *Writes table* também é atualizada com o ponteiro para o endereço armazenado na *Write bitmap table*. A *current table* é atualizada fazendo a verificação dos registradores que haviam sido armazenados anteriormente, e adicionando os novos registradores utilizados. A *start table* não é modificada, pois o primeiro operando de entrada será o resultado da primeira operação e o segundo operando já estava contido na *start table*.

As instruções subsequentes seguem a mesma lógica de funcionamento das duas descritas acima. Com as tabelas preenchidas, é possível salvar a configuração na *cache* e utilizá-la para execução na unidade funcional reconfigurável, fazendo a decodificação das tabelas. Na subseção 3.3.2, será demonstrado o algoritmo utilizado pelo tradutor binário para criação das tabelas.

### 3.3.2 Algoritmo de Tradução Binária

O algoritmo descrito a seguir é a versão utilizada para construção do módulo do tradutor binário. É uma versão baseada em [BECK FILHO, 2008].

Este algoritmo serve como base do funcionamento do TB utilizado, e possui os seguintes passos:

1. **Decodificação das instruções:** Decodifica a instrução que está sendo executada no processador e determina seu grupo. Indica o uso de operandos imediatos e instruções especiais como lui e store. Se a instrução que está sendo executada é

inválida, o algoritmo vai para o passo 7 e fecha a configuração.

2. **Análise de dependência de dados** (escolha da linha): Para escolher qual a linha da UFR que será alocada a instrução é necessário verificar as dependências de dados da mesma, utilizando a *Write Bitmap Table* e a *Read Bitmap Table*. Caso não haja local a ser alocado sem violação de dependência de dados é necessário ir para o passo 7 e fechar a configuração.

3. **Determinação de Recursos Livres** (escolha da coluna): Quando não há dependências verificadas, a instrução é alocada na próxima coluna. Caso já haja algum dado executando é alocada a próxima coluna, e assim sucessivamente, através da *Resource Table*. Caso não houver mais recursos livres o algoritmo vai para o passo 7 e fecha a configuração.

4. **Atualização das tabelas de bitmap**: Atualiza as tabelas *Write Bitmap Table*, *Read Bitmap Table* e *Resource Table* na posição determinada nos passos 2 e 3.

5. **Atualização da Context Table**: Verifica se o registrador ainda não está na tabela e adiciona-o. Se o operador for de leitura e não estiver na tabela é necessário adicioná-lo na *Start Table*. Se o operando for imediato e ainda não estiver na tabela é necessário adicioná-lo a *Immediate Table*. Caso alguma das tabelas estiver completa, é necessário ir ao passo 7 para fechar a configuração.

6. **Atualização das Tabelas da Fase de Reconfiguração**: Neste passo é necessário atualizar a *Function Table*, *Read Table* e *Write Table* na posição determinada nos passos 2 e 3.

7. **Fechamento de uma configuração**: Indica o encerramento de uma configuração. Caso a configuração tenha o número mínimo de instruções necessárias para ser salva ela é escrita na *cache* de configurações, caso contrário ela é descartada e uma nova configuração é criada.

### 3.4 Cache de Configurações

A *cache* de configurações é onde são armazenadas as configurações a serem carregadas para a unidade funcional reconfigurável. Na implementação atual do sistema em VHDL a *cache* é completamente associativa, ou seja, qualquer endereço pode ser mapeado em qualquer posição da *cache*. A política de substituição utilizada é a *Fist in, Fist out* (FIFO).

### 3.5 Funcionamento do Sistema

O sistema reconfigurável DIM possui as seguintes fases execução: Fase de Detecção, Fase de Reconfiguração e Fase de Execução.

Na fase de detecção, o tradutor binário (TB) analisa as instruções que estão sendo executadas no PPG e as transforma em uma configuração da arquitetura reconfigurável. Neste processo, o tradutor binário extrai o paralelismo em nível de instrução (ILP) das instruções que estão sendo traduzidas. Ao fim de cada processo de tradução o TB armazena a configuração em uma memória, chamada *cache* de configurações. Uma configuração é indexada na *cache* de configurações pelo *program counter* (PC) da primeira instrução a ser executada, facilitando a verificação da existência da configuração respectiva a aquele trecho de código na *cache* de configurações. Uma configuração é composta de: endereços dos registradores utilizados, valores imediatos, controle das operações que serão realizadas na unidade reconfigurável e o PC da última e primeira instrução executada na configuração.

A fase de reconfiguração começa quando o *program counter* da instrução que está sendo buscada na memória de instruções é igual ao PC inicial de alguma configuração armazenada na *cache*. Quando isto ocorre, indica que existe uma configuração na *cache* que deverá ser executada na unidade reconfigurável. Desta forma, o fluxo de execução passa do PPG para a UFR.

Por conseguinte, os seguintes passos são executados:

- Carregam-se os valores dos registradores e os valores imediatos utilizados nas operações para o contexto de entrada.

- Selecionam-se os dados de entrada nas unidades funcionais para que seja feito corretamente. Esta seleção ocorre por multiplexadores que estão nas entradas das unidades funcionais.

- Configuram-se os multiplexadores para que as entradas e saídas dos dados a serem computados sejam calculadas e salvas de forma correta.

Por fim, a fase de execução é a fase onde os dados são calculados de forma combinacional na unidade funcional reconfigurável, para que posteriormente sejam salvos no banco de registradores ou memória.

# **4 ACOPLAGEMTO E VALIDAÇÃO DO SISTEMA DIM**

Este capítulo descreve a contribuição deste trabalho, ou seja, o processo de acoplamento e validação funcional da arquitetura reconfigurável DIM descrita em VHDL. As seções seguintes demonstram o histórico de implementações dos módulos em VHDL, a metodologia utilizada para validação do sistema, assim como os testes e modificações realizadas no sistema DIM.

## **4.1 Histórico de implementação**

Trabalhos anteriores sobre o sistema DIM propuseram a descrição dos seguintes módulos do sistema em VHDL: Controle da UFR, tradutor binário e unidade funcional reconfigurável. Em [LAZZAROTTO, 2011] foi proposto o desenvolvimento do tradutor binário. A Unidade Funcional Reconfigurável utilizada foi desenvolvida em [GEGLER, 2007]. O controle para esta UFR foi descrito em [NAZAR, 2008]. O processador de propósito geral utilizado foi o MIPS R3000, que utiliza a ISA MIPS I, sua descrição em VHDL foi extraída da uma biblioteca de IPs [MINIMIPS, 2008].

Todos os módulos supracitados foram desenvolvidos em VHDL a fim de verificar o funcionamento dos blocos do sistema em nível de ciclo. Desta forma, é possível, além de se obter uma alta precisão de simulação, extrair resultados em relação ao desempenho, potência e área do sistema.

Entretanto, apesar de todos os blocos estarem separadamente validados, existe a necessidade da integração e validação do sistema como um todo. Desta forma, este trabalho se baseia nestas implementações e propõe o acoplamento destes módulos, ajustando os problemas oriundos da integração e validando o sistema DIM em VHDL.

## 4.2 Metodologia de Acoplamento e Validação Funcional do Sistema

Figura 6: Fluxograma mostrando a forma de validação funcional do sistema

A metodologia utilizada para validar o sistema pode ser vista no fluxograma da Figura 6. Criam-se aplicações em linguagem de programação C, e compila-se o código para linguagem de máquina MIPS. Após a compilação, a aplicação é simulada, desta forma é possível verificar os problemas de execução e corrigi-los. Quando todos os problemas de uma determinada aplicação forem corrigidos, cria-se uma nova aplicação para validação. Após qualquer modificação no sistema todas as aplicações desenvolvidas anteriormente são testadas novamente para validar a modificação.

Devido à alta complexidade dos módulos descritos em VHDL, onde o somatório do número de linhas da descrição é de 9522 linhas, foi necessário um estudo em cada um destes para verificar o funcionamento do sistema. Este estudo foi realizado a partir da

análise dos arquivos VHDL dos módulos em separado. Por conseguinte, verificou-se o funcionamento do sistema completo, acoplando todos os módulos. O código é dividido nos seguintes grandes blocos: tradutor binário, unidade funcional reconfigurável, processador miniMIPS, memória RAM e o controle para a unidade funcional reconfigurável.

Para o processo de validação, utilizou-se o ambiente ISE 10.1 da Xilinx, usando IPs de memória e de divisor disponíveis na ferramenta. O software utilizado para simulação é o Modelsim, que carrega os módulos das bibliotecas do software ISE.

Na sequência deste capítulo serão mostradas todas as aplicações testadas e as devidas modificações realizadas na validação funcional do sistema. Considerou-se o sistema válido, após inúmeros testes que inclui a execução das seguintes aplicações: somas simples, somas de vetores, somas de matrizes e um algoritmo de ordenação e dados *bubble sort*.

### 4.3 Aplicação de soma de elementos em um loop For

Devido a sua maior simplicidade em relação às outras aplicações, primeiramente escolheu-se realizar a análise sobre a aplicação de uma soma vetorial. O algoritmo possui uma soma de duas variáveis, armazenando o resultado em um vetor. Além disso, ele computa a soma de duas variáveis, armazenando o resultado em outra variável. As operações são realizados dentro de um *loop for* para que após a primeira iteração do *loop* (realizada no MIPS) fosse possível executar as instruções das próximas iterações do *loop* na UFR. O código da aplicação pode ser visto na Figura 7.

```

#define SIZE 10

unsigned a[SIZE] = {1, 1, 1, 1, 1, 1, 1, 1, 1, 1};

unsigned b = 2;

unsigned c = 3;

unsigned d = 4;

unsigned e = 5;

int main(void) {

int i;

for(i=0; i<SIZE; i++) {

a[i] = c + e;

b = d + e;

}

while(1);

}

```

Figura 7: Aplicação soma de elementos em um loop For

Analizando esta aplicação verificou-se que ao configurar a unidade funcional, o registrador selecionado no multiplexador de entrada da ALU estava incorreto. Percebeu-se

que o problema estava na montagem incorreta da *Read table* (seção 3.3.1).

A Figura 8 mostra um exemplo de execução da instrução addu Rc,Rd,Rc, com o erro encontrado. A seleção no multiplexador de entrada é feita para o registrador Ra ao invés de Rc, causando uma execução incorreta de uma instrução addu Rc,Rd,Ra ao invés da instrução addu Rc,Rd,Rc. O controle deste multiplexador de entrada é realizado pela *read table* que é armazenada na configuração.

Figura 8: Exemplo de seleção incorreta do multiplexador na entrada da ALU da UFR

#### 4.3.1 Atualização da *Read table*

A primeira configuração armazenada na *cache*, da aplicação mostrada na seção 4.3, é mostrada a seguir:

```

lw $5, %gp_rel(e)($28)

addu $3, $3, $2

lui $2, %hi(a)

```

A *context\_table\_current* da presente configuração é mostrada na Tabela 2.

Tabela 2: *Context\_table\_current* para a primeira configuração

| <i>context_table_current</i> |    |   |   |        |       |

|------------------------------|----|---|---|--------|-------|

| 5                            | 28 | 3 | 2 | rel(e) | hi(a) |

A *read\_table*, a partir da primeira configuração, é mostrada na Tabela 3.

Tabela 3: *Read\_table* na primeira configuração antes da modificação

| <i>read_table</i> |    |  |  |  |  |

|-------------------|----|--|--|--|--|

| *1                | *3 |  |  |  |  |

| *0                | *5 |  |  |  |  |

Percebe-se que há dados incorretos na primeira coluna da primeira linha, e na primeira coluna da segunda linha da *read\_table*. Os ponteiros para a *context\_table\_current* armazenados na tabela são para a posição 1 e 0 respectivamente, apontando portanto para os registradores 28 e 5. Este erro causa uma seleção incorreta do multiplexador de entrada da unidade reconfigurável, sendo executadas as instruções addu \$3,\$28,\$2 e lui \$5,%hi(a), diferentemente do que era esperado para a configuração.

O mesmo problema foi verificado na segunda configuração armazenada, sendo mostrada a seguir:

```

addiu $2,$2,%lo(a)

add $2,$4,$2

add $5,$6,$5

```

A *context\_table\_current* desta configuração é mostrada na Tabela 4.

Tabela 4: *Context\_table\_current* para a segunda configuração

| <i>context_table_current</i> |   |   |   |       |  |

|------------------------------|---|---|---|-------|--|

| 2                            | 4 | 5 | 6 | lo(a) |  |

A *read\_table* da segunda configuração é mostrada na Tabela 5.

Analizando a *read\_table*, percebe-se que esta tabela possui um erro na quarta coluna da primeira linha, armazenando um ponteiro para a posição 0 da *context\_table\_current* ao invés da posição 2 que seria a correta. Por conseguinte, a instrução executada na UFR é add \$5,\$6,\$2, pois o registrador armazenado na posição 0 da *context\_table\_current* é o \$2 e não o \$5 como era esperado.

Devido aos erros verificados, necessitou-se a correção através da atualização da *read\_table* gerada no tradutor binário. Este erro ocorre devido ao fato da *context\_table\_current*

Tabela 5: *Read\_table* para a segunda configuração antes da modificação

| <i>read_table</i> |    |    |    |

|-------------------|----|----|----|

| *0                | *4 | *3 | *0 |

| *1                | *0 |    |    |

ainda não estar atualizada quando é feita a atualização da *read table*. Assim, fez-se necessária a atualização da *read\_table* após a modificação na *context\_table\_current*. A modificação feita no código VHDL do bloco de dependência de dados do TB, é mostrada na Figura 18 do apêndice A.

Ainda foi necessário garantir que os operandos *op1*, *op2* e *opw*, somente sejam modificados na borda de subida do *clock*. Isto se deve ao fato de que o tradutor binário é baseado em um *pipeline*, desta forma é preciso manter os operandos inalterados durante o ciclo para que a atualização nas tabelas seja realizada conforme o esperado.

Desta forma, a *read\_table* passou a ser atualizada corretamente. A Tabela 6 mostra a *read\_table* da primeira configuração após as modificações, e a Tabela 7 mostra a *read\_table* da segunda configuração após as modificações feitas no código VHDL do sistema DIM.

Tabela 6: *Read\_table* da primeira configuração depois da modificação

| <i>read_table</i> |    |  |  |

|-------------------|----|--|--|

| *2                | *3 |  |  |

| *3                | *5 |  |  |

Tabela 7: *Read\_table* da segunda configuração depois da modificação

| <i>read_table</i> |    |    |    |

|-------------------|----|----|----|

| *0                | *4 | *3 | *2 |

| *1                | *0 |    |    |

Conforme ilustrado nas tabelas, pode-se perceber que as tabelas passaram a ser atualizadas de forma correta e, a execução destas configurações na unidade funcional reconfigurável foi realizada com êxito.

### 4.3.2 Problema no incremento do número de instruções

Ao ocorrer um travamento no *pipeline* do processador devido a alguma dependência de dados das instruções que estão nos estágios do *pipeline*, o tradutor binário adiciona várias vezes a instrução localizada no segundo estágio (*Instruction Decode*) na configuração. A Figura 9 mostra o problema encontrado na simulação. Percebe-se que o sinal *pc\_out* (última instrução adicionada à configuração), mantém-se em 684 por dois ciclos

de *clock* devido a dependência de dados no processador, entretanto o número de instruções na configuração passa de 3 para 4, como pode ser visto no último sinal da Figura 9 (*num\_i*). Este incremento no número de instruções na configuração ocasiona a adição da mesma instrução mais uma vez à configuração, ocasionando uma execução incorreta desta configuração na UFR.

Figura 9: Problema no incremento do número de instruções

Para correção deste problema, necessitou-se adicionar um sinal para verificar se o PC do processador modificou em relação ao valor do ciclo anterior. Após esta modificação, só há uma atualização no número de instruções quando houver uma instrução diferente do ciclo anterior.

Verificou-se que a modificação necessária não poderia ocorrer no primeiro estágio do tradutor binário (Decodificação), visto que o TB descartava algumas configurações que deveriam ser armazenadas na *cache*. Isto ocorre porque o tradutor binário é bloqueado quando a última instrução da configuração a ser armazenada mantém-se a mesma por mais de um ciclo de *clock*, por conseguinte, o TB é impossibilitado de armazenar a configuração na *cache*.

Portanto, percebeu-se que a modificação necessitava ser realizada no estágio de dependência de dados do tradutor binário. O TB passou a não ser desabilitado durante o "congelamento" do PPG, apenas não se atualizam as tabelas no caso em que a mesma instrução se mantenha por mais de um ciclo. Desse modo é possível armazenar todas as configurações válidas na *cache* de acordo com os critérios mostrados na subseção 3.3.2.

A Figura 19 do apêndice A mostra o trecho de código modificado no estágio de dependência de dados, necessário para correção do problema descrito acima.

Com as modificações descritas nas subseções 4.3.1 e 4.3.2, a aplicação mostrada na Figura 7 passou a funcionar corretamente, executando-a na unidade funcional reconfigurável de forma correta.

## 4.4 Aplicação de soma de elementos em vários loops For

A partir das modificações realizadas no VHDL para o correto funcionamento da aplicação mostrada na seção 4.3, criou-se uma aplicação semelhante apenas replicando o laço for por mais 5 vezes, Figura 10. Esta aplicação foi criada com o intuito de verificar o armazenamento de várias configurações na *cache* e analisar a política de substituição utilizada (FIFO).

```

#define SIZE 10

unsigned a[SIZE] = {1, 1, 1, 1, 1, 1, 1, 1, 1, 1};

unsigned b = 2;

unsigned c = 3;

unsigned d = 4;

unsigned e = 5;

int main(void) {

int i;

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

for(i=0; i<SIZE; i++){

a[i] = c + e;

b = d + e;}

while(1);

}

```

Figura 10: Aplicação soma de elementos em vários loops For

A política de substituição (FIFO) funcionou conforme o esperado, quando não existem mais blocos disponíveis na *cache* de configuração e existe uma requisição de armazenagem de uma nova configuração, ocorre a substituição da configuração que está armazenada a mais tempo na *cache*. Entretanto, observou-se a ocorrência de gravação duplicada na *cache*. Em alguns casos, uma mesma configuração era armazenada em duas posições

distintas da *cache*, causando um baixo aproveitamento da mesma.

#### 4.4.1 Gravação duplicada de uma configuração

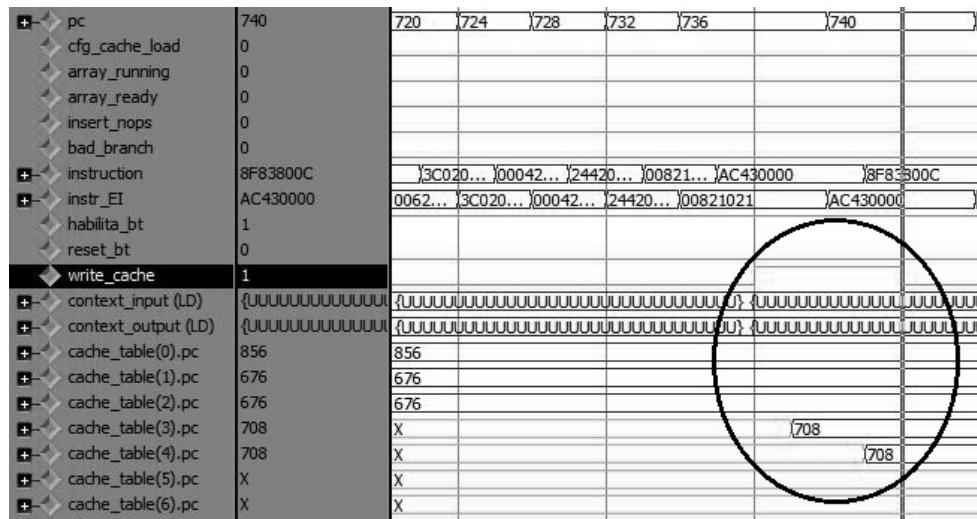

Observa-se que os sinais *cache\_table*, mostrados na Figura 11, indicam os índices das configurações armazenadas na *cache* de configurações. Percebe-se que em alguns casos a configuração era gravada duplicadamente na *cache* como pode ser observado na Figura 11. A *cache\_table(1)* e *cache\_table(2)* possuem a mesma configuração, assim como em *cache\_table(3)* e *cache\_table(4)*. Notou-se que o sinal de *write\_cache* possui nível lógico alto por mais de um ciclo de *clock* em configurações onde a última instrução é mantida por mais de um ciclo devido as dependências de dados no *pipeline* do miniMIPS.

|                     | pc               | 740              | 720              | 724              | 728              | 732              | 736              | 740              |  |

|---------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|--|

| cfg_cache_load      | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| array_running       | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| array_ready         | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| insert_nops         | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| bad_branch          | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| instruction         | 8F83800C         |                  | 3C020...         | 00042...         | 24420...         | 00821...         | AC430000         | 8F83800C         |  |

| instr_EI            | AC430000         |                  | 0062...          | 3C020...         | 00042...         | 24420...         | 00821021         | AC430000         |  |

| habilita_bt         | 1                |                  |                  |                  |                  |                  |                  |                  |  |

| reset_bt            | 0                |                  |                  |                  |                  |                  |                  |                  |  |

| write_cache         | 1                |                  |                  |                  |                  |                  |                  |                  |  |

| context_input (LD)  | {XXXXXXXXXXXXXX} |  |

| context_output (LD) | {XXXXXXXXXXXXXX} |  |

| cache_table(0).pc   | 856              | 856              |                  |                  |                  |                  |                  |                  |  |

| cache_table(1).pc   | 676              | 676              |                  |                  |                  |                  |                  |                  |  |

| cache_table(2).pc   | 676              | 676              |                  |                  |                  |                  |                  |                  |  |

| cache_table(3).pc   | 708              | X                |                  |                  |                  |                  | (708)            |                  |  |

| cache_table(4).pc   | 708              | X                |                  |                  |                  |                  | (708)            |                  |  |

| cache_table(5).pc   | X                | X                |                  |                  |                  |                  |                  |                  |  |

| cache_table(6).pc   | X                | X                |                  |                  |                  |                  |                  |                  |  |

Figura 11: Simulação com duplicação de configuração na *cache*

Para correção deste problema foi necessário garantir que o sinal de *write\_cache* (Figura 11) mantivesse em nível lógico alto por apenas um ciclo de *clock*. Então, adicionou-se um sinal (*sig\_write\_cache*) para que o sinal *write\_cache* seja acionado apenas uma vez em uma determinada configuração. A modificação realizada no código VHDL do sistema pode ser vista na Figura 20 localizada no apêndice A.

#### 4.5 Aplicação *Bubble Sort*

A terceira aplicação utilizada para validar a arquitetura reconfigurável foi o algoritmo de ordenação de dados *bubble sort*, Figura 12. Esta aplicação foi testada e validada por ser um algoritmo simples, eficaz e de grande utilização para ordenação de dados.

```

int vetor[10] = {10,9,8,7,6,5,4,3,2,1};

int tamanho = 10;

int main(void){

int aux;

int i;

int j;

int r;

for(i=tamanho-1; i >= 1; i--) {

for(j=0; j < i ; j++) {

if(vetor[j]>vetor[j+1]) {

aux = vetor[j];

vetor[j] = vetor[j+1];

vetor[j+1] = aux;

}

}

}

while(1);

}

```

Figura 12: Aplicação de um Bubble Sort

Analizando as simulações, encontraram-se problemas no controle da unidade funcional reconfigurável e no tradutor binário. Nas subseções a seguir serão descritos os problemas e suas respectivas soluções.

#### 4.5.1 Busca na *cache* de configurações com PC incorreto

Quando há uma execução na unidade funcional reconfigurável são inseridas instruções NOP no PPG, porém seu PC continua incrementando enquanto a execução na UFR está ocorrendo. O comportamento correto deve somente atualizar o PC do miniMIPS com o endereço da última instrução da configuração em execução. Em vista disso, a máquina de estados responsável pela busca de uma configuração na *cache* deve estar "congelada" enquanto houver uma execução na UFR, não detectando nenhuma nova configuração.

Contudo, percebeu-se que a máquina de estados buscava novas configurações mesmo quando ainda havia execução de uma configuração anterior na UFR, ocasionando uma busca com o PC incorreto. Necessitou-se modificar a máquina de estados que controla a UFR. Enquanto há uma execução na unidade reconfigurável, é preciso garantir que o controle só irá realizar uma nova busca na *cache* de configurações depois da atualização do PC do processador com o valor apropriado, ou seja, após o término da execução atual na UFR. Desta forma, foi adicionada uma condição para que a busca de uma nova configuração, pelo controle da unidade reconfigurável, somente seja realizada quando não

houver uma execução ativa na UFR. A modificação realizada no VHDL é mostrada no apêndice A (Figura 21).

#### 4.5.2 Continuação de uma configuração mesmo após execução na UFR

Na fase de detecção, o tradutor binário verifica a instrução que está sendo executada no processador para armazená-la em uma configuração. Quando há instruções executando na unidade funcional reconfigurável, o TB deve encerrar a configuração conforme o passo 7 na subseção 3.3.2.

Contudo, verificou-se que ao haver uma execução na unidade reconfigurável o tradutor binário apenas não atualiza as tabelas da presente configuração, ao invés de encerrá-la. Em vista disso, há uma perda de instruções a serem inseridas na configuração, acarretando em uma execução incorreta desta configuração na UFR.

Para correção deste problema, fez-se necessário o tratamento da configuração como inválida quando há uma execução na unidade funcional reconfigurável. Então, toda vez que se inicia a execução na UFR, o TB encerra a configuração atual (conforme descrito no passo 7 na subseção 3.3.2) e cria uma nova configuração após o término da execução na UFR.

A modificação pode ser vista na Figura 22 do apêndice A, onde foi adicionada uma condição para quando houver uma execução na UFR, o estágio de decodificação identifique e indique a configuração como inválida.

#### 4.5.3 Configurações criadas na inicialização do programa

Instruções de inicialização da aplicação são indesejadas de serem armazenadas na *cache* de configurações, visto que este código é somente executado uma vez e a execução de configurações na UFR somente ocorre na segunda execução de um determinado trecho de código. Assim, o armazenamento de configurações com instruções de inicialização torna o sistema menos eficiente, visto que são armazenadas configurações na *cache* que não serão utilizadas.

Ao analisar diversas aplicações, percebeu-se um padrão de inicialização. As instruções de inicialização eram executadas até o *program counter* obter o valor de 600. Com isto, conseguiu-se garantir que não houvesse criação de configurações na inicialização da aplicação. A Figura 22 do apêndice A, mostra a modificação realizada no código do estágio

de decodificação do TB.

Após as modificações mostradas nas subseções 4.5.1, 4.5.2 e 4.5.3, a aplicação de *bubble sort* funcionou corretamente, ordenando o vetor conforme esperado. Estas modificações foram testadas também nas aplicações mostrada nas seções 4.3 e 4.4, funcionando corretamente e validando as modificações feitas no código do sistema DIM.

## 4.6 Soma de Matrizes

A seguinte aplicação, mostrada na Figura 13, a ser validada funcionalmente é uma soma de matrizes. Criou-se essa aplicação com o intuito de verificar o funcionamento do sistema com uma maior computação de dados na unidade funcional reconfigurável.

```

#define SIZE 10

int main(void) {

int i, j;

for(i=0; i<SIZE; i++) {

for(j=0; j<SIZE; j++) {

c[i][j] = a[i][j] + b[i][j];

}

}

while(1);

}

```

Figura 13: Aplicação de soma de matrizes

Verificou-se que esta aplicação não funcionou conforme o esperado, salvando um dado inconsistente no banco de registradores do processador.

### 4.6.1 Registrador com dado inconsistente

Encontrou-se uma inconsistência no dado de um registrador do banco de registradores do miniMIPS. Esta inconsistência estava sendo causada por uma tentativa de gravação de dados simultâneos entre processador e unidade funcional reconfigurável em um registrador do banco de registradores do processador. Isto ocorre devido ao fato do processador MIPS possuir quatro instruções no *pipeline* a ser executadas quando ocorre um *cache hit* de uma configuração. Em vista disso, há uma execução simultânea na UFR e no MIPS, por conseguinte, há uma tentativa de gravação no banco de registradores do PPG simultaneamente pela UFR e pelo estágio de *write back* do MIPS. Com a chegada de ambos os dados simultaneamente, o registrador armazenava apenas um dado inconsistente ('X'), ao invés de armazenar o valor correto.

Fez-se necessário, adicionar um contador de três ciclos para garantir que haja o esvaziamento do *pipeline* do processador antes de realizar a carga do banco de registradores do PPG para o contexto de entrada da UFR. Garantindo-se o esvaziamento do *pipeline* do processador, trata-se o problema de gravação simultânea entre PPG e UFR, assim como, há uma garantia que os valores inseridos no contexto de entrada da unidade reconfigurável, a partir do banco de registradores do PPG, estão corretos.

O número de ciclos de espera para o esvaziamento do *pipeline* do processador, foi calculado a partir da premissa de que há um ciclo para a troca de estados na FSM que controla a unidade reconfigurável, assim que uma configuração válida for buscada na *cache*. Então, fazem-se necessários mais três ciclos para garantir que os quatro estágios de *pipeline* do processador em execução, computem seus dados antes da carga do contexto de entrada da UFR, a partir do banco de registradores do PPG.

A correção feita pode ser vista na Figura 23 no apêndice A, realizando-se a modificação no estágio de *WAIT PIPE* da FSM do controle da unidade reconfigurável.

Após todas as modificações realizadas no código VHDL da arquitetura DIM, validou-se funcionalmente as aplicações executadas.

# 5 *RESULTADOS*

Neste capítulo serão apresentados os resultados obtidos a partir da síntese lógica do sistema DIM em VHDL. Inicialmente será mostrada a metodologia utilizada para obtenção dos resultados. Em seguida será feita uma análise da potência, desempenho e área do sistema em nível de hardware.

## 5.1 Metodologia

Para obter resultados do sistema DIM, realizou-se a síntese lógica do mesmo na ferramenta Encounter RTL Compiler. O Encounter RTL Compiler é a ferramenta de projeto do ambiente CADENCE responsável pela síntese lógica dos circuitos projetados em VHDL ou Verilog. A síntese lógica consiste no mapeamento e otimização de um *netlist* genérico, formado a partir de flip-flops, multiplexadores e portas lógicas booleanas, para uma tecnologia alvo a ser utilizada.