Universidade Federal de Santa Maria - UFSM

Centro de Tecnologia - CT

Curso de Engenharia de Computação

ELC1054 - Projeto de Sistemas Digitais Integrados

# Implementação ASIC para um Compressor JPEG

Luis Felipe de Deus – [felipe.deus@ecomp.ufsm.br](mailto:felipe.deus@ecomp.ufsm.br)

Nathanael Luchetta – [nathanael.luchetta@ecomp.ufsm.br](mailto:nathanael.luchetta@ecomp.ufsm.br)

Tiago Knorst – [tiago.knorst@ecomp.ufsm.br](mailto:tiago.knorst@ecomp.ufsm.br)

# Agenda

- Introdução

- Objetivo

- Metodologia

- Desenvolvimento

- Resultados

- Conclusões

- Trabalhos Futuros

# Introdução

- Sistemas Embarcados: Restrições !

# Introdução

- Sistemas Embarcados: Restrições !

- Área

- Energia

- Tempo

# Objetivo

- Comprimir imagens do formato *bitmap* -> *JPEG*

- *.bmp (MB)* -> *.jpeg (KB)* com perdas baixas.

# Objetivo

- Reduzir o uso de CPU e memória.

# Objetivo

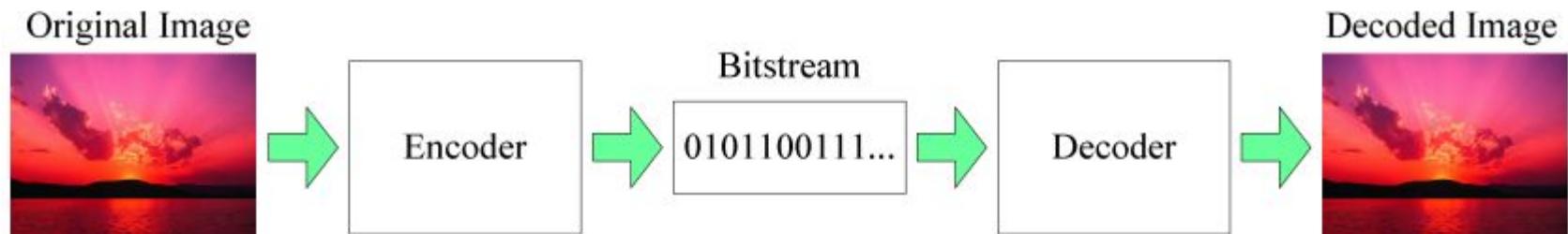

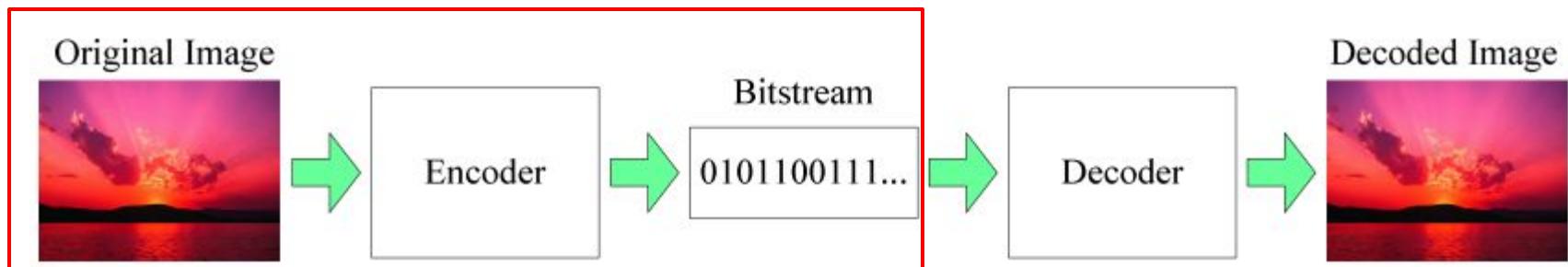

- Fluxo de codificação simplificado

Fonte: WEI, W. An Introduction to Image Compression, 2013.

# Objetivo

- Fluxo de codificação simplificado

Fonte: WEI, W. An Introduction to Image Compression, 2013.

# Metodologia

- Linguagens:

- VHDL – VHSIC *Hardware Description*;

- C;

- Matlab.

- Ferramentas:

- ISE Design Suite – Xilinx;

- ModelSim – Mentor Graphics;

- Encounter RTL – Cadence Design Systems;

- NCLaunch - Cadence Design Systems;

- Encounter Digital Implementation - Cadence Design Systems;

- Matlab.

# Metodologia

- *Datasets:*

- Comparação com implementação de Krepa (2009);

- Métrica de desempenho:

- Comparação com ARM Cortex A9;

- Comparação com ASIC de Pastuszak (2005) ;

# Metodologia

- Vetores de teste: imagem Lena.bmp

Tamanhos:

- 8x8;

- 64x64;

- 512x512.

# Desenvolvimento

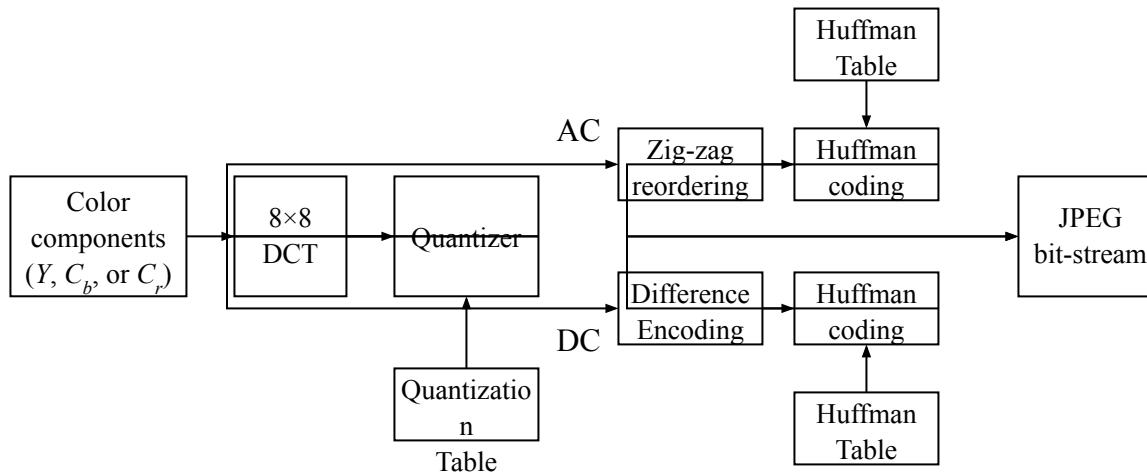

- Fluxo de compressão JPEG

Fonte: HUANG, J. The JPEG Standard. 2008.

# Desenvolvimento

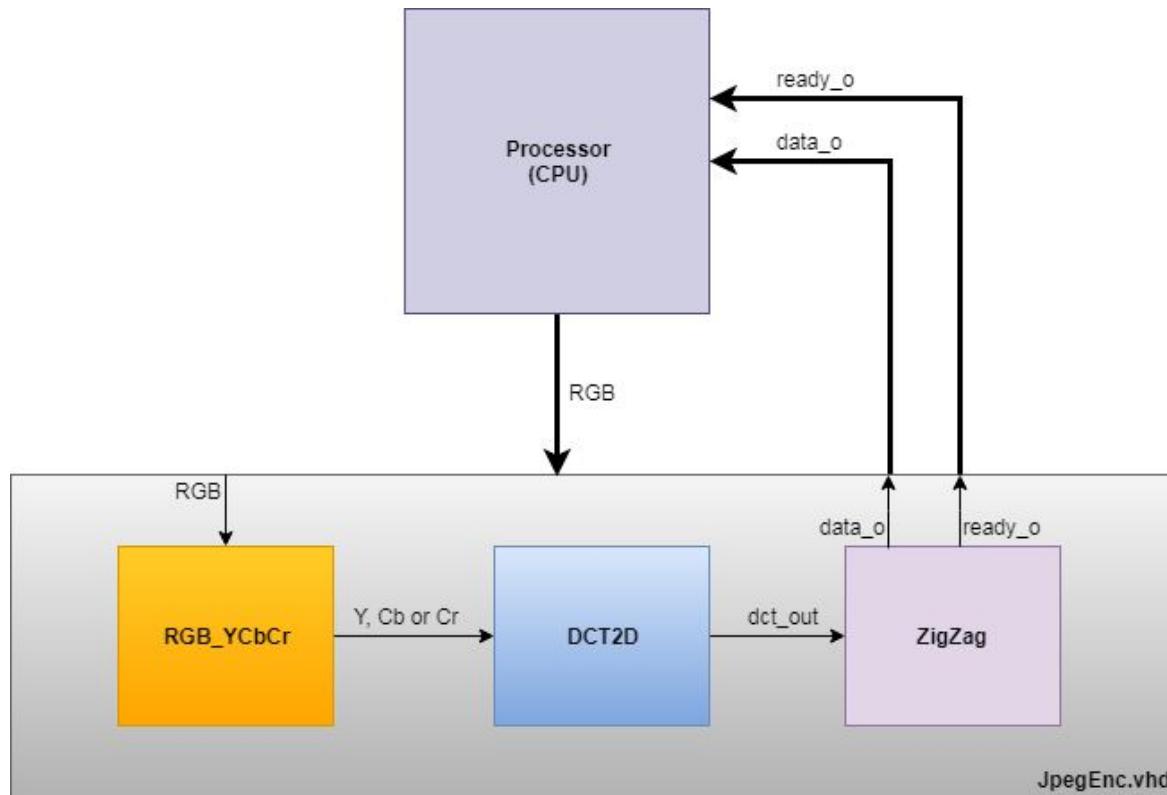

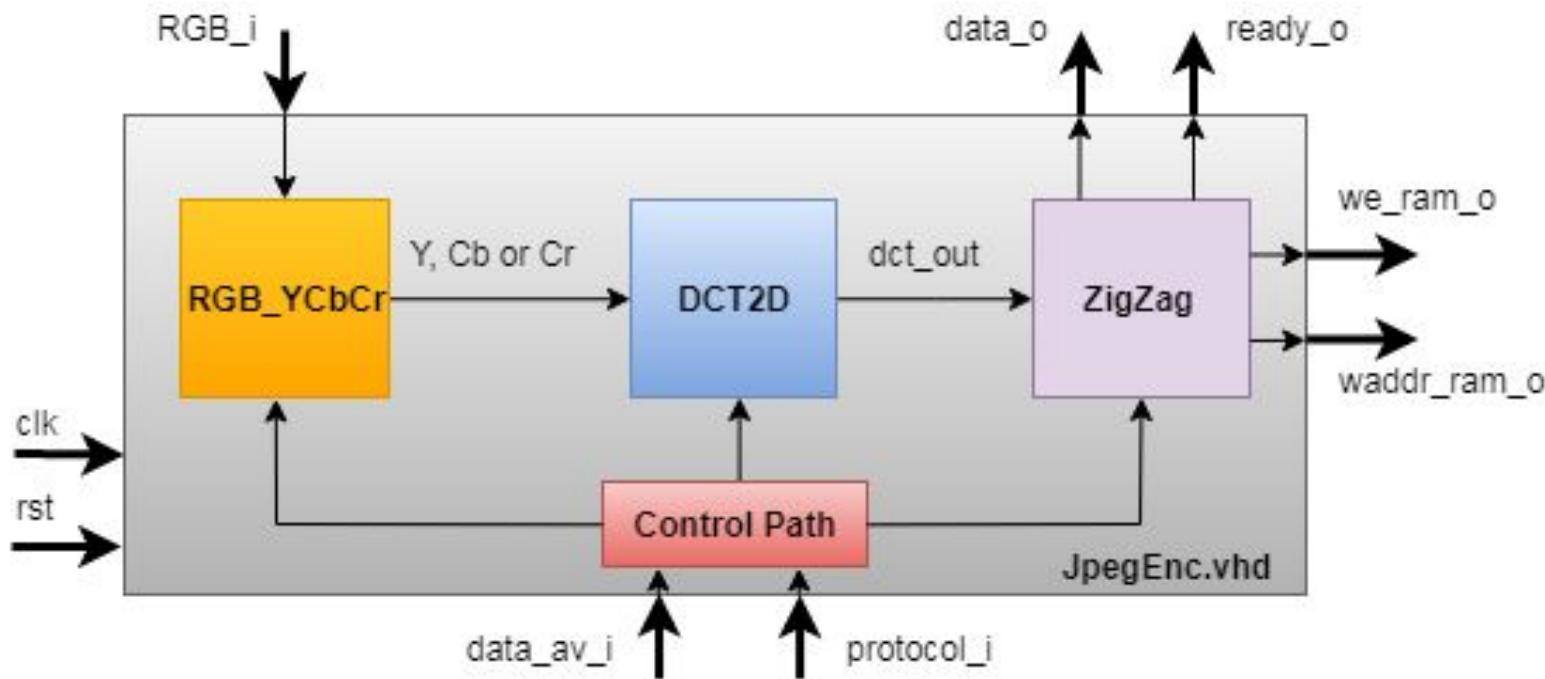

- Diagrama de blocos

# Desenvolvimento

- Fluxo de dados do projeto

# Desenvolvimento

- *Control Path*

- Pipeline;

- Sequencial.

- *Data Path*

- $RGB\_YCbCr$ ;

- $DCT2D$ ;

- *Scanner ZigZag*.

# Resultados

- Análise de tempo: 200MHz

| <b>Resultados de performance</b> |                   |

|----------------------------------|-------------------|

| <b>Vetor</b>                     | <b>Tempo (μs)</b> |

| <b>Lena: 8x8</b>                 | 3,75              |

| <b>Lena: 64x64</b>               | 47,2              |

| <b>Lena: 512x512</b>             | 2760              |

# Resultados

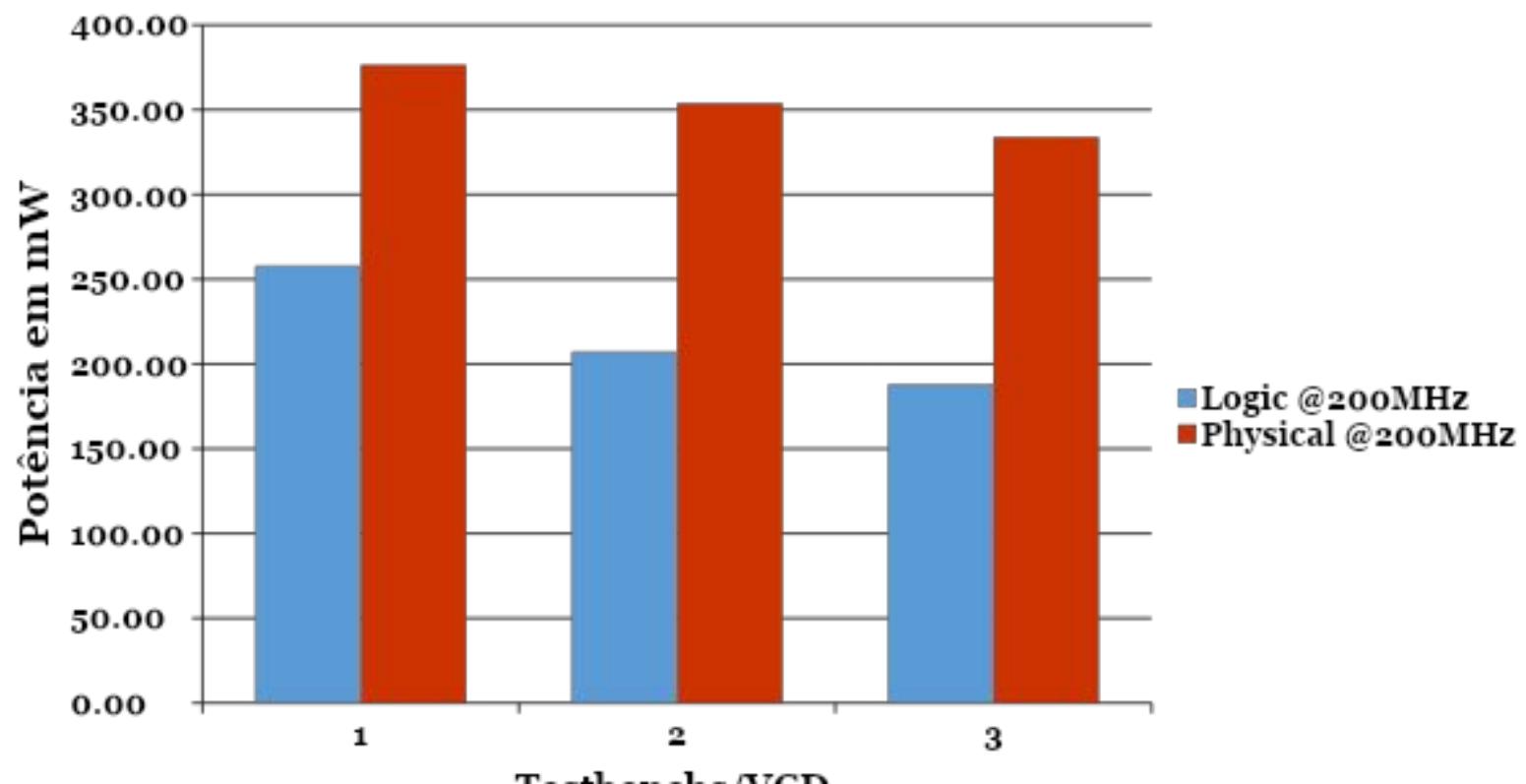

- Análise de potência sobre vetores de teste

## Evolução da potência em função do VCD

# Resultados

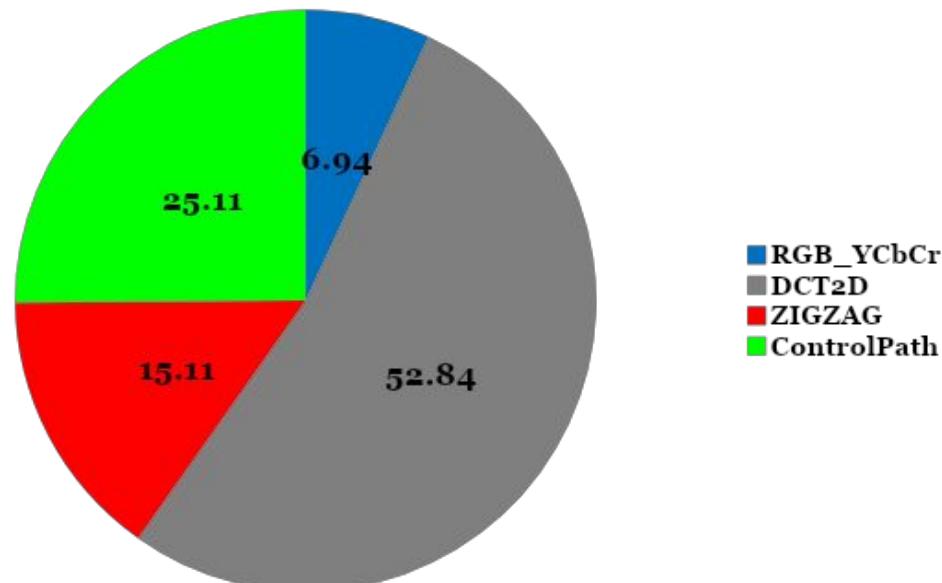

- Distribuição de área (*die*) no *chip* JpegEnc: Área = 0,988 mm<sup>2</sup>

Distribuição de Área no *Chip* JpegEnc

# Comparação: ARM Cortex A9

- Apple: iPhone 4s

- Samsung: Galaxy S2

# Comparação

| <b> vetor de teste: Lena 512x512</b> |                           |                            |                                 |

|--------------------------------------|---------------------------|----------------------------|---------------------------------|

| <b>Dispositivo</b>                   | <b>JpegEnc</b><br>(180nm) | <b>ASIC</b><br>(Pastuszak) | <b>ARM Cortex A9</b><br>(45 nm) |

| <b>Área (mm<sup>2</sup>)</b>         | 0,988                     | -                          | 16,092                          |

| <b>Potência (W)</b>                  | 0,334                     | -                          | 7,323                           |

| <b>Freq. (MHz)</b>                   | 200                       | 200                        | 1000                            |

| <b>Tempo (ms)</b>                    | 2,76                      | 10,01                      | 580,56                          |

# Custo x Benefício em relação ARM Cortex A9

| <b>Dispositivo</b>                       | <b>Área (mm<sup>2</sup>)</b> | <b>Potência (W)</b> |

|------------------------------------------|------------------------------|---------------------|

| <b>ARM Cortex A9 (45 nm)</b>             | 16,092                       | 7,32316             |

| <b>JpegEnc (180 nm)</b>                  | 0,988                        | 0,33404             |

| <b>Acréscimo JpegEnc sobre Cortex A9</b> | 6,14%                        | 4,56%               |

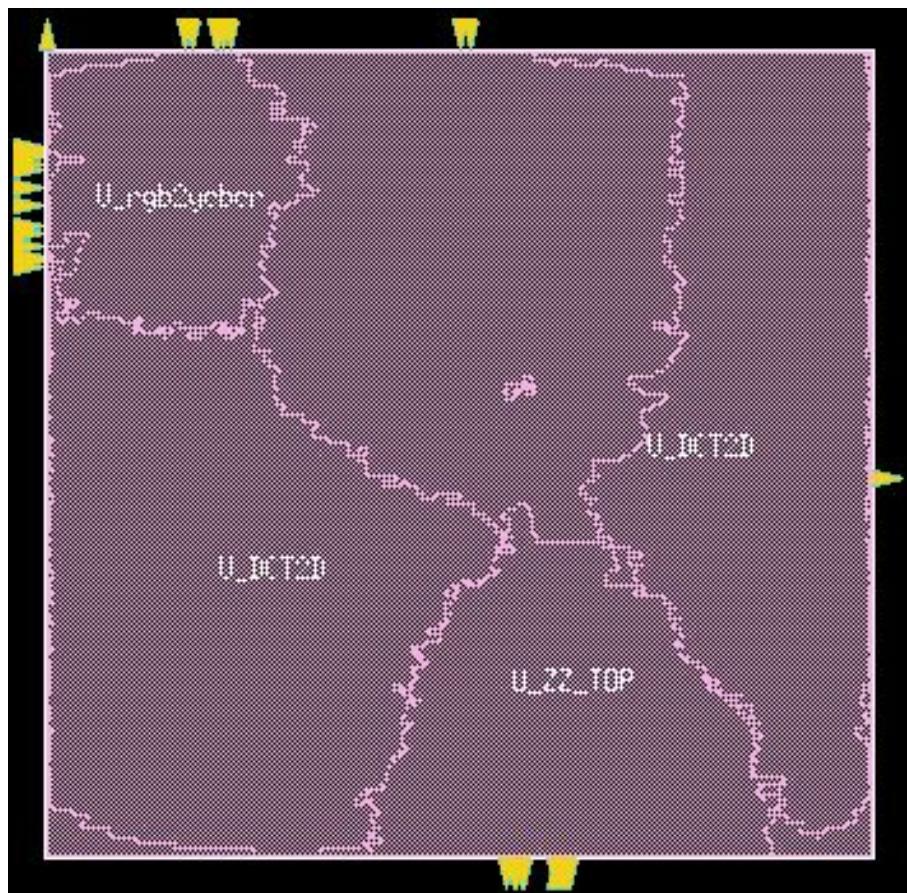

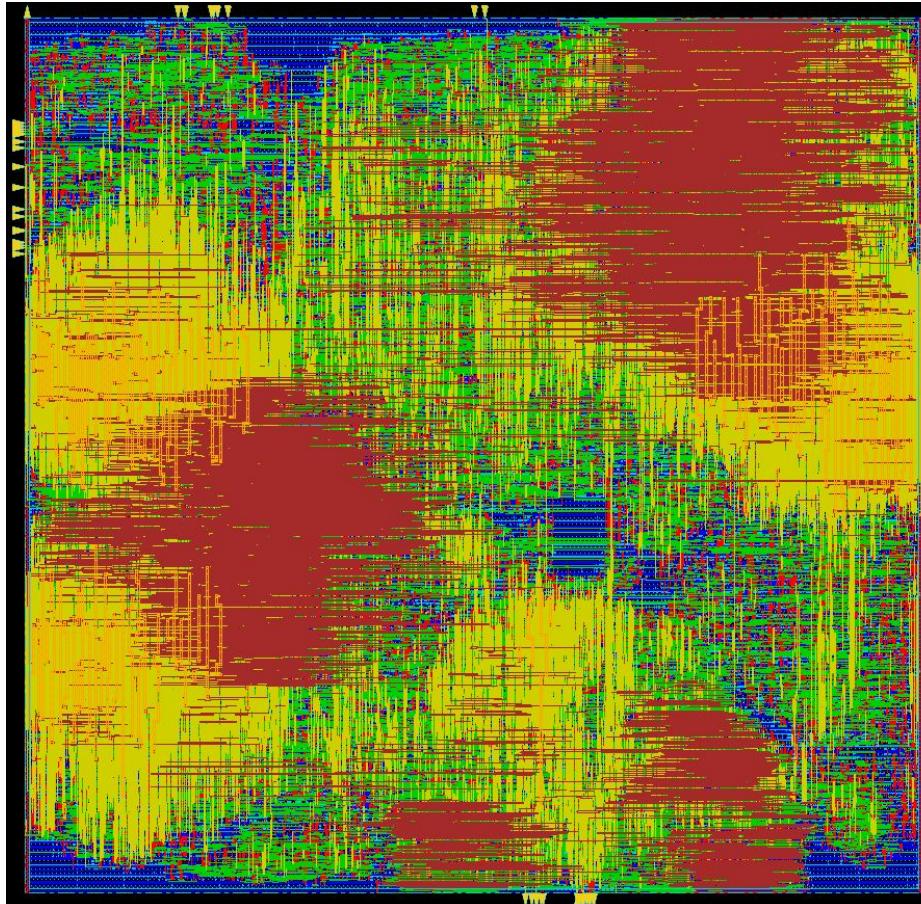

# Resultados

- *Layout* físico do *chip* JpegEnc: Área= 0,988 mm<sup>2</sup>

Fonte: Encouter Digital Implementation - Cadence

# Conclusões

- Trabalhar em cima de um objetivo concreto é de suma importância;

- Decisões iniciais de projeto são muito importantes;

- O *chip* JpegEnc é economicamente viável;

- Alto Custo x Benefício ao processador ARM Cortex A9.

# Trabalhos Futuros

- Implementação dos blocos: Quantizador e codificação Huffman;

- Controle *pipeline* para maximizar o desempenho;

- Implementação Encoder e Decoder JPEG no mesmo *chip*.

# Obrigado pela Atenção !

## Perguntas?

Luis Felipe de Deus – [felipe.deus@ecomp.ufsm.br](mailto:felipe.deus@ecomp.ufsm.br)

Nathanael Luchetta – [nathanael.luchetta@ecomp.ufsm.br](mailto:nathanael.luchetta@ecomp.ufsm.br)

Tiago Knorst – [tiago.knorst@ecomp.ufsm.br](mailto:tiago.knorst@ecomp.ufsm.br)